8∢

| Device                         |          |                  |                    |                        |                      | ,                   |

|--------------------------------|----------|------------------|--------------------|------------------------|----------------------|---------------------|

| <i>Type</i><br><i>Feature</i>  | TMS 9900 | TMS 9900-40      | SBP 9900A          | TMS 9980A/<br>TMS 9981 | TMS 9985             | TMS 9940            |

| Number of bytes<br>addressable |          | 65k              | 65k                | 16k                    | 65k<br>256 RAM       | 2k EPROM<br>128 RAM |

| Number of Interrupts           |          | 16               | 16                 | 5                      | 5                    | 4                   |

| Number of Pins                 |          | 64               | 64                 | 40                     | 40                   | 40                  |

| Power Supply<br>Requirements   | +5,      | 5, +12           | 500 Ma<br>(Note 1) | +5,                    | +5                   | +5                  |

| Technology                     | I        | N-MOS            | $I^2L$             | N-MOS                  | N-MOS                | N-MOS               |

| Environmental<br>(Temperature) | 0        | -70°C            | - 55-125°C         | 0-70°C                 | 0-70°C               | 0-70°C              |

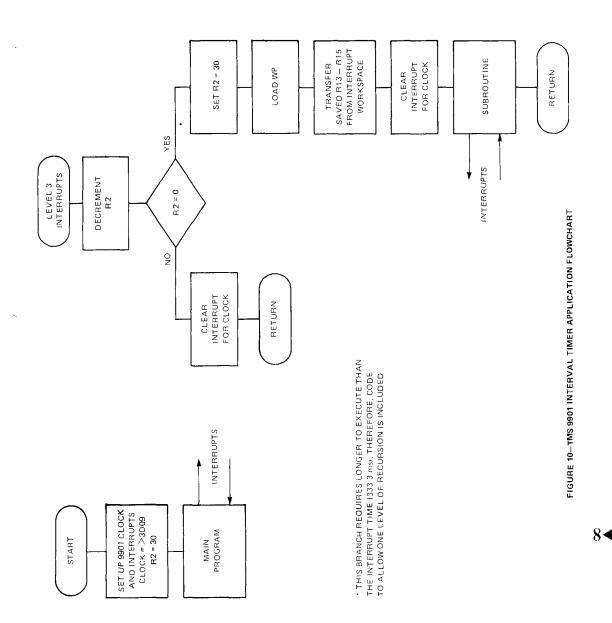

| Clock Rate                     | 3.3 MHz  | 4 MHz            | 3 MHz              | 10MHz                  | 5 MHz                | 5 MHz               |

| Relative Thruput               | 1.0      | 1.3              | 0.9                | 0.6                    | 0.65-0.8<br>(Note 2) | 1.2                 |

| Number of Address<br>Bus Lines |          | 15               | 15                 | 14                     | 16                   | (Note 3)            |

| Number of Data Bus<br>Lines    | 1        | 16               | 16                 | 8                      | 8                    | (Note 3)            |

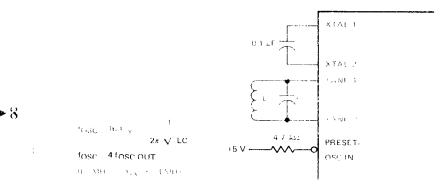

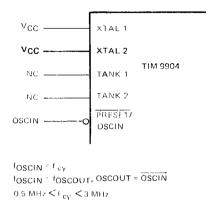

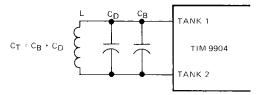

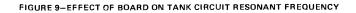

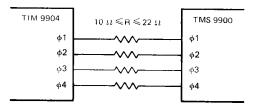

| Clock                          | TIT      | v <b>1 99</b> 04 | SN54LS124          | On chip                | On chip              | On chip             |

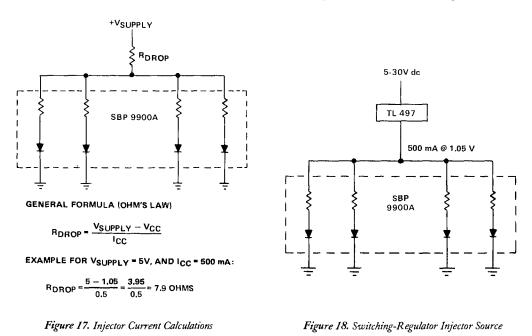

Note 1: Voltage for the SBP 9900A is 1.5 to 30 volts with a series resistor.

Note 2: The relative thruput is 0.65 with an off-chip RAM and 0.8 with an on-chip RAM.

Note 3: There are 32 general purpose pins which can be programmed for I/O. While the memory and data buses are not available, 8 address bits are accessible for CRU I/O expansion.

#### FAMILY DESCRIPTION

The TMS 9900 micrprocessor is a single-chip 16-bit central processing unit (CPU) produced using N-channel silicon-gate MOS technology. The instruction set of the TMS 9900 includes the capabilities offered by full minicomputers. The unique memory-to-memory architecture features multiple register files, resident in memory, which allow faster response to interrupts and increased programming flexibility. The separate bus structure simplifies the system design effort. Texas Instruments provides a compatible set of MOS and TTL memory and logic function circuits to be used with a TMS 9900 system. The system is fully supported by software and a complete prototyping system.

There is a TMS 9900-40 part designed for 4-MHz operation. Refer to the separate "-40" (dash forty) electrical specification tables for exact characteristics.

▶8

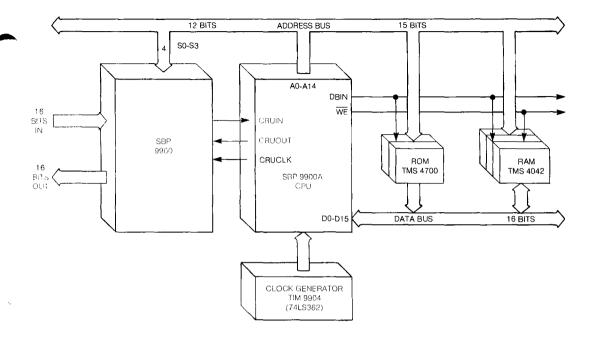

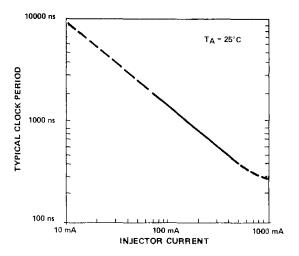

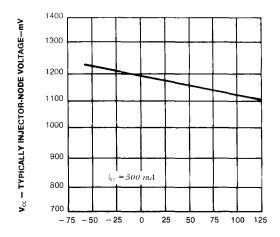

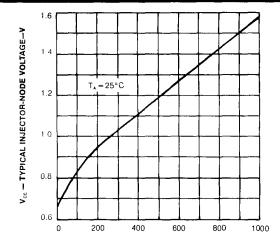

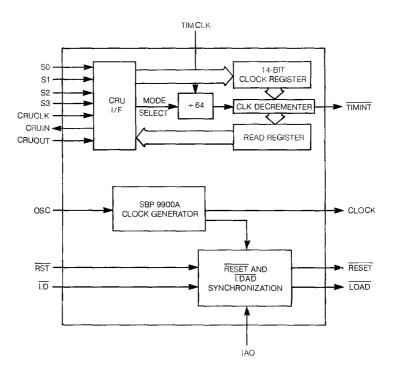

The SBP 9900A is basically the same as the TMS 9900 but it employs  $I^2L$  technology to enhance environmental specifications. It is a static, bipolar microprocessor operating from a single phase clock over the frequency range from 0 to 3 MHz. The I/O is fully TTL compatible so that no special peripheral circuits are required. The power supply is specified as a single input injector current which may be varied over the range from 10 mA to 1 A with a corresponding change in speed (described in the specific SBP 9900A section). The architecture is the same for the SBP 9900A as the TMS 9900 with minor differences in clock and control lines.

Software compatibility with other 9900 microprocessor family members provides a common body of hardware/software within Texas Instruments 990 minicomputer family.

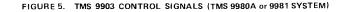

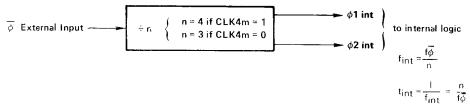

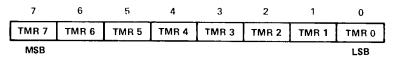

The TMS 9980A/TMS 9981 is another software-compatible member of TI's 9900 family of microprocessors. Designed to minimize the system cost for smaller systems, the TMS 9980A/TMS 9981 is a single-chip 16-bit central processing unit (CPU) which has an 8-bit data bus, on-chip clock, and is packaged in a 40-pin package. The instruction set of the TMS 9980A/TMS 9981 includes the capabilities offered by full minicomputers and is exactly the same as the 9900's.

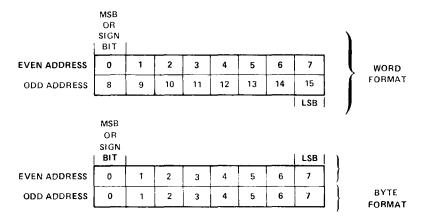

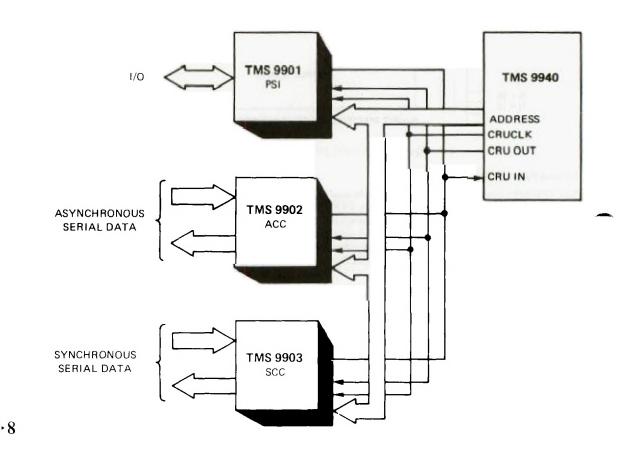

The TMS 9940 is a single-chip, 16-bit microprocessor containing a CPU, memory (RAM and EPROM/ROM), and extensive I/O. Except for four instructions which do not apply to the TMS 9940 microcomputer configuration, the TMS 9940 instruction set matches that of the TMS 9900 and includes capabilities offered by *minicomputers*. In addition, the TMS 9940 instruction set includes two instructions which facilitate manipulation of binary coded decimal (BCD) data, and a single-word load-interrupt-mask (LIIM) instruction.

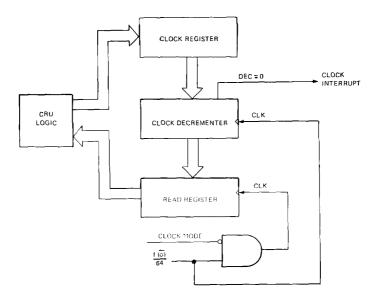

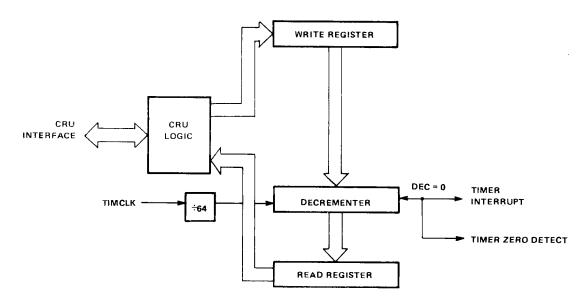

The unique memory-to-memory architecture features multiple register files, resident in the RAM, which allow faster response to interrupts and increased programming flexibility. The memory consists of 128 bytes of RAM and 2048 bytes of EPROM. The TMS 9940 implements four levels of interrupts including an internal decrementer which can be programmed as a timer or an event counter. All members of the TMS 9900 family of peripheral circuits are compatible with the TMS 9940. The TMS 9940 is fully supported by software and hardware development systems and by factory applications engineers and technical answering services.

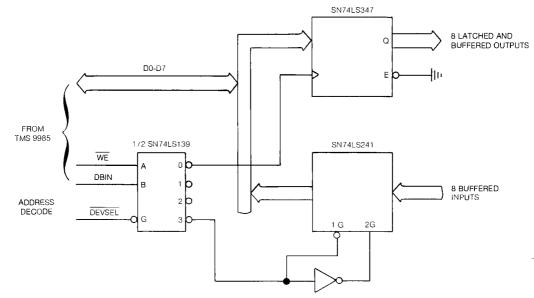

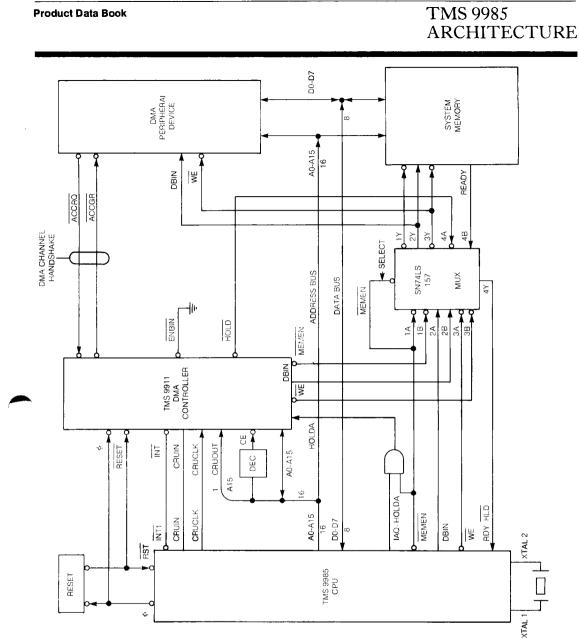

The TMS 9985 is a software compatible member of TI's 9900 family of microprocessors and microcomputers and contains a 16-bit CPU, 256 bytes of RAM, on chip timer/event counter, external 16-bit address bus and 8-bit data bus, and is in a 40-pin package. The instruction set of the TMS 9985 includes the capabilities offered by full minicomputers and is exactly the same as the TMS 9940 microcomputer's. The unique memory-to-memory architecture features multiple register files, resident in memory, which allows faster response to interrupts and increased programming flexibility. In addition, the TMS 9985 has excellent I/O flexibility with CRU, memory mapped I/O and direct memory access.

#### COMMON KEY FEATURES

- 16-Bit Architecture

- 69 Powerful Instructions Include: Multiply and Divide

5 Addressing Modes

Bit, Byte, and Word Addressing

One, Two and Three Word Instructions

- Rapid Hardware Context Switching

- Multiple 16-Word Register Files (Workspaces) Reside in Memory

- Separate I/O, Memory and Interrupt Bus Structures

- Programmed and DMA I/O Capability

- · Communications Register Unit (CRU) for Low and Medium Speed Devices

- Efficient Memory-to-Memory Architecture

- Extended Operations (XOP) Feature Allows Users to Augment the Instruction Set

- Maskable Vectored Priority Interrupts for Multiprogramming Requirements

- Software Compatible with 990 Minicomputer Family

#### KEY FEATURES OF SPECIFIC DEVICES

#### TMS 9900

- 3.3-MHz Speed (4.0 MHz Speed for the TMS 9900-40)

- Up to 65,536 Bytes of Memory

- 16 Prioritized Interrupts

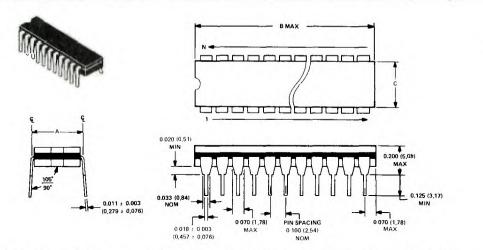

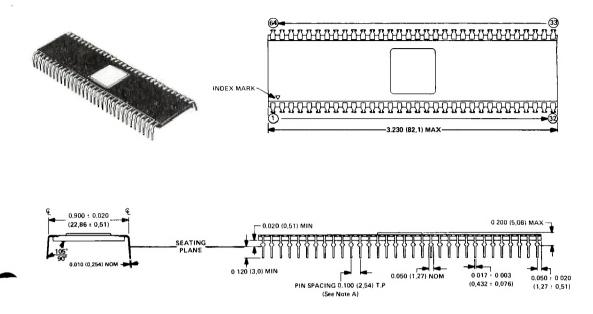

- 64-Pin Package

- N-Channel Silicon-Gate Technology

- 0-70°C Ambient Temperature Range

- Directly TTL Compatible I/O

#### SBP 9900A

- 3-MHz Speed

- Up to 65,536 Bytes of Memory

- 16 Prioritized Interrupts

- 64-Pin Package

- I<sup>2</sup>L Technology

- -55 to 125°C Ambient Temperature Range

- Single dc Power Supply

- Directly TTL Compatible I/O

#### TMS 9980A/TMS9981

- 10-MHz Speed

- Up to 16,384 Bytes of Memory

- 8-Bit Memory Data Bus

- 4 Prioritized Interrupts

- On-Chip 4-Phase Clock Generator

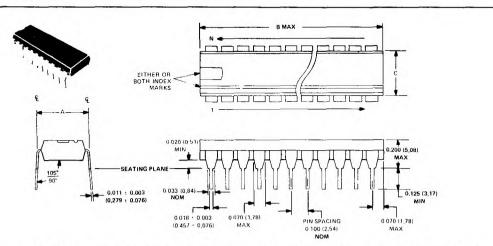

- 40-Pin Package

- N-Channel Silicon-Gate Technology

- 0-70°C Ambient Temperature Range

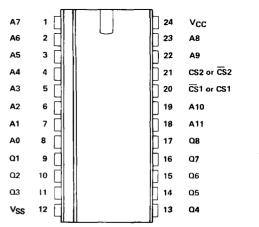

#### TMS 9980A / TMS 9981 Differences

The TMS 9980A and the TMS 9981, although very similar, have several differences of which the user should be aware.

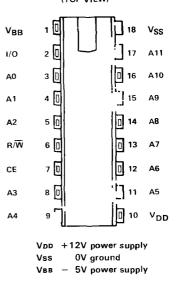

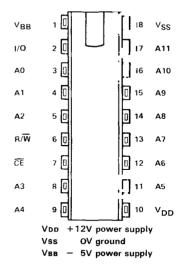

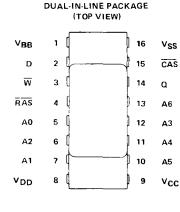

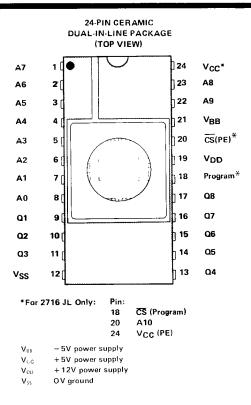

1. The TMS 9980A requires a  $V_{BB}$  supply (pin 21) while the TMS 9981 has an internal charge pump to generate  $V_{BB}$  from  $V_{\rm CC}$  and  $V_{\rm PD}.$

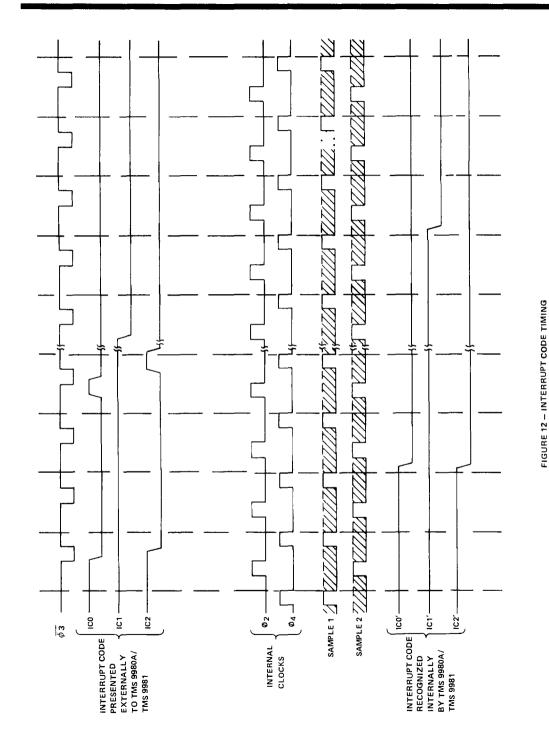

2. The TMS 9981 has an optional on-chip crystal oscillator in addition to the external clock mode of the TMS 9980A.

3. The pin-outs are not the same for D0-D7, INT0-INT2, and  $\overline{\phi3}$ .

#### TMS 9985

▶8

- 5-MHz Speed

- Up to 65,536 Bytes of Memory

- 8-Bit Memory Data Bus

- 5 Prioritized Interrupts

- 40-Pin Package

- N-Channel Silicon-Gate Technology

- 0-70°C Ambient Temperature Range

- On Chip Timer/Event Counter

- 256 Bits of RAM on Chip

- Separate Memory, I/O and Interrupt Bus Structures

- On Chip Programmable Flags (16)

- Multiprocessor System Interface

- Single 5-Volt Supply

- Speed Selected Versions

## INTRODUCTION

#### TMS 9940

- 5-MHz Speed

- 2048 Bytes of EPROM or ROM

- 128 Bytes of RAM

- 4 Prioritized Interrupts

- 40-Pin Package

- N-Channel Silicon-Gate Technology

- 0-70°C Ambient Temperature Range

- On-Chip Timer/Event Counter

- 32 Bits General Purpose I/O

- 256 Bits I/O Expansion

- Multiprocessor System Interface

- Single 5-Volt Power Supply

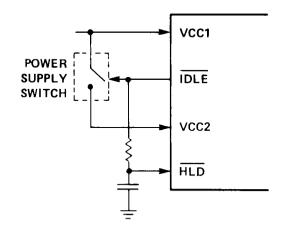

- Power Down Capability for Low Standby Power

- Easy Test Function

- Offered as either an EPROM device as a mask ROM device

- Speed Selected Versions

#### Organization of CPU Data Manuals and Instruction Set

Data manuals for the five CPU's in the 9900 family are reproduced in this section with the TMS 9900 first, followed by the SBP 9900A, TMS 9980A/81, and TMS 9940 data manuals. Following this there is an abbreviated version of the TMS 9985 manual. Since the information regarding the instruction set is common to all of the CPU's, it has been removed from the individual manuals and is printed at the end of this section.

# TMS 9900

▶8

#### 1. INTRODUCTION

#### 1.1 DESCRIPTION

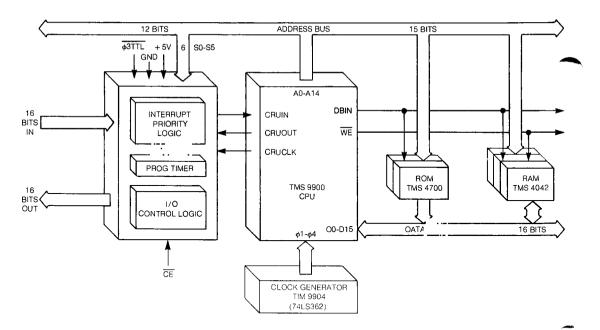

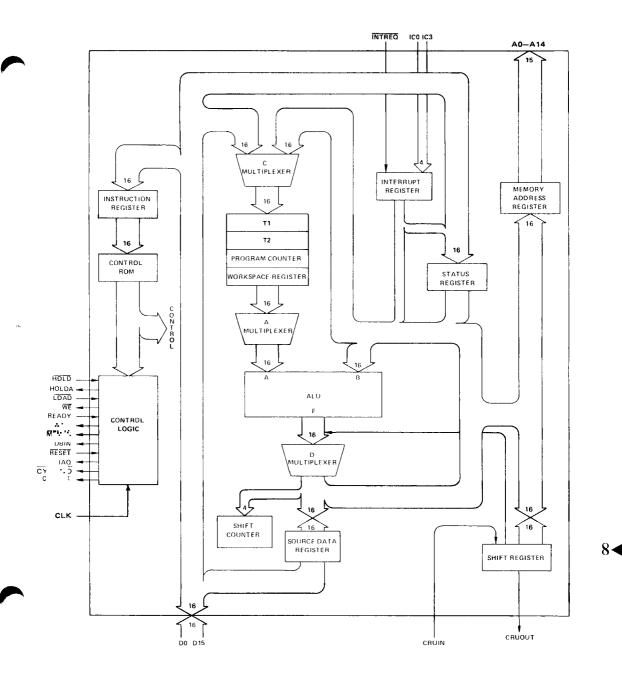

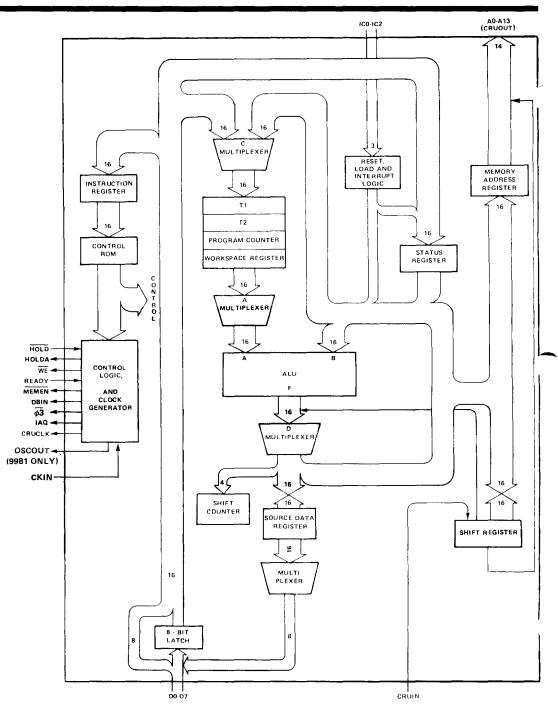

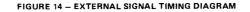

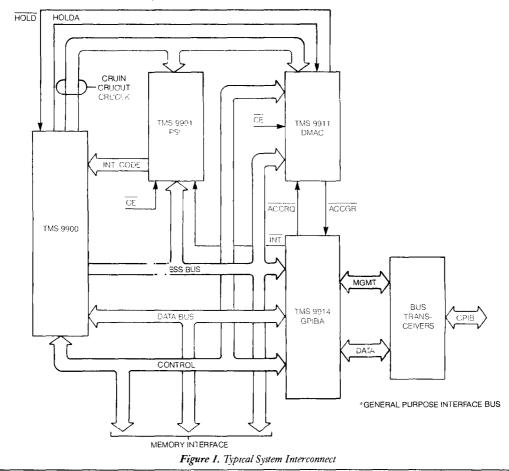

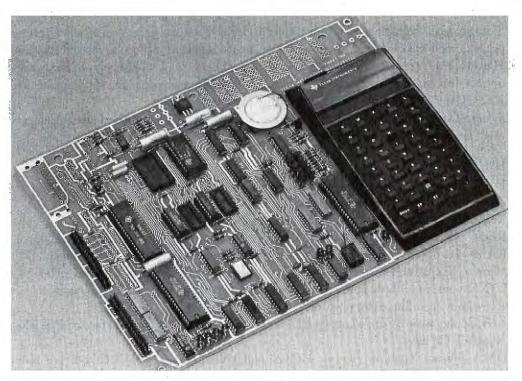

The TMS 9900 microprocessor is a single-chip 16-bit central processing unit (CPU) produced using N-channel silicon-gate MOS technology (see Figure 1). The instruction set of the TMS 9900 includes the capabilities offered by full minicomputers. The unique memory-to-memory architecture features multiple register files, resident in memory, which allow faster response to interrupts and increased programming flexibility. The separate bus structure simplifies the system design effort. Texas Instruments provides a compatible set of MOS and TTL memory and logic function circuits to be used with a TMS 9900 system. The system is fully supported by software and a complete prototyping system.

#### 1.2 KEY FEATURES

- 16-Bit Instruction Word

- Full Minicomputer Instruction Set Capability Including Multiply and Divide

- Up to 65,536 Bytes of Memory

- 3.3 MHz Speed

- Advanced Memory-to-Memory Architecture

- Separate Memory, I/O, and Interrupt-Bus Structures

- 16 General Registers

- 16 Prioritized Interrupts

- Programmed and DMA I/O Capability

- N-Channel Silicon-Gate Technology

#### 2. ARCHITECTURE

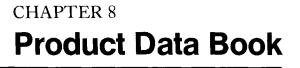

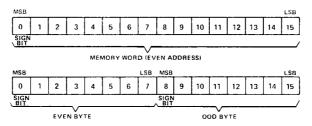

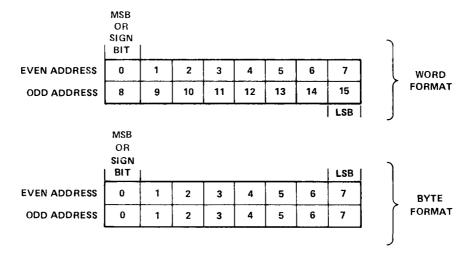

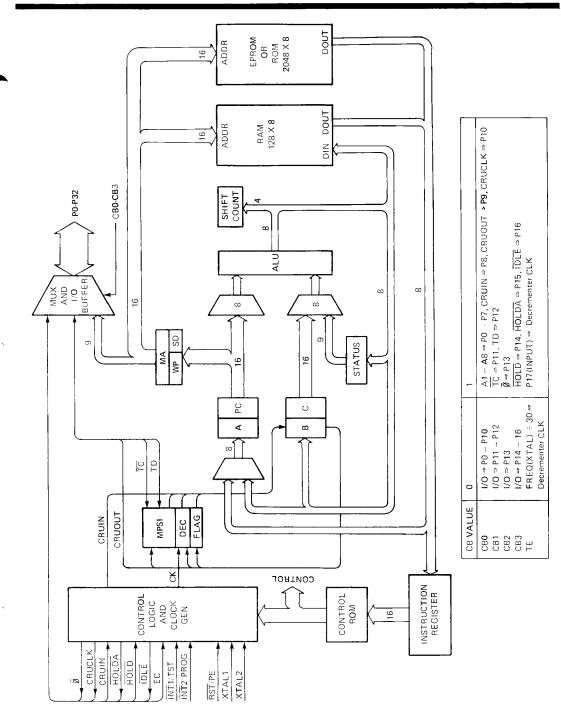

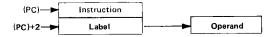

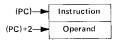

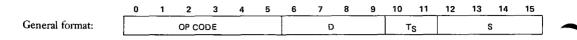

The memory word of the TMS 9900 is 16 bits long. Each word is also defined as 2 bytes of 8 bits. The instruction set of the TMS 9900 allows both word and byte operands. Thus, all memory locations are on even address boundaries and byte instructions can address either the even or odd byte. The memory space is 65,536 bytes or 32,768 words. The word and byte formats are shown below.

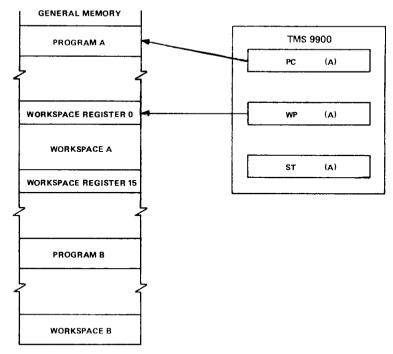

#### 2.1 REGISTERS AND MEMORY

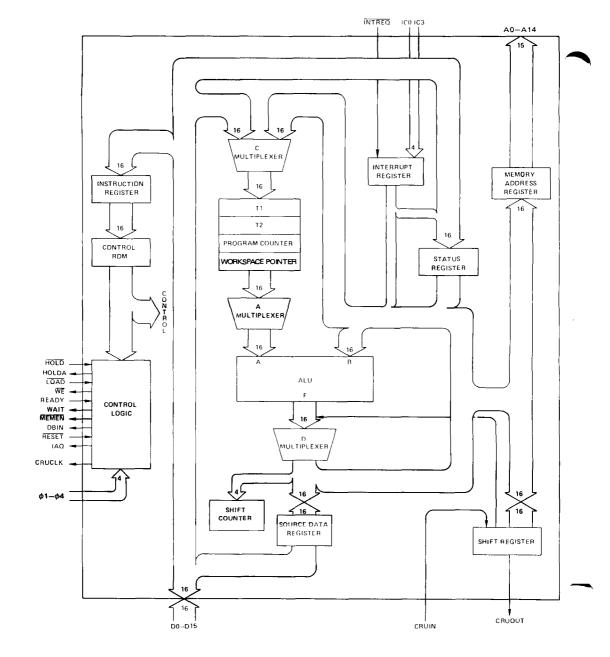

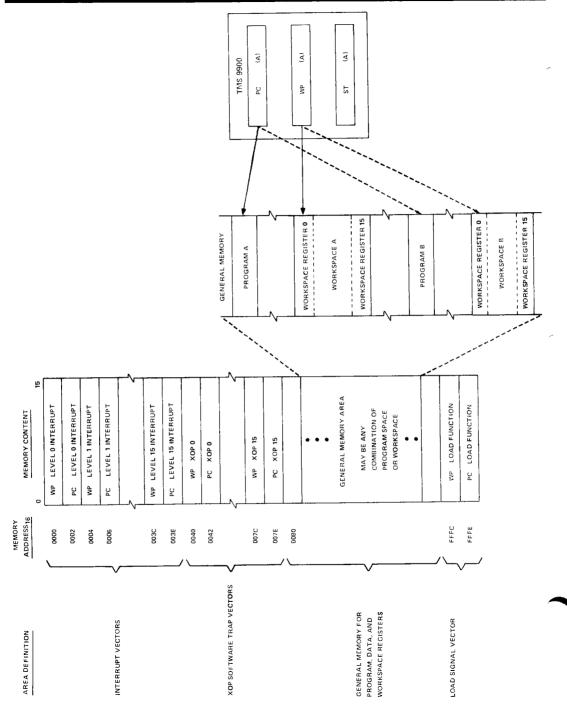

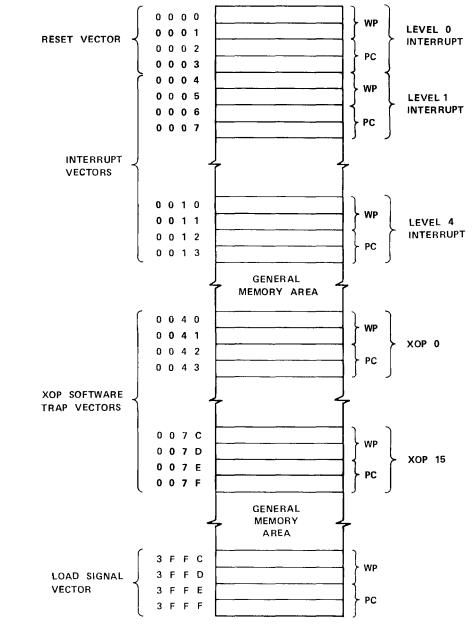

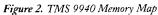

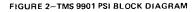

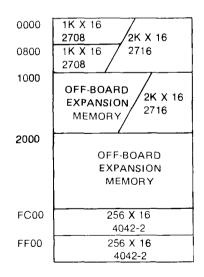

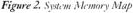

The TMS 9900 employs an advanced memory-to-memory architecture. Blocks of memory designated as workspace replace internal-hardware registers with program-data registers. The TMS 9900 memory map is shown in Figure 2. The first 32 words are used for interrupt trap vectors. The next contiguous block of 32 memory words is used by the extended operation (XOP) instruction for trap vectors. The last two memory words, FFFC<sub>16</sub> and FFFE<sub>16</sub>, are used for the trap vector of the LOAD signal. The remaining memory is then available for programs, data, and workspace registers. If desired, any of the special areas may also be used as general memory.

Product Data Book

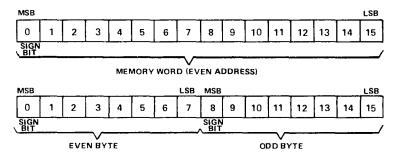

## I MS 9900 ARCHITECTURE

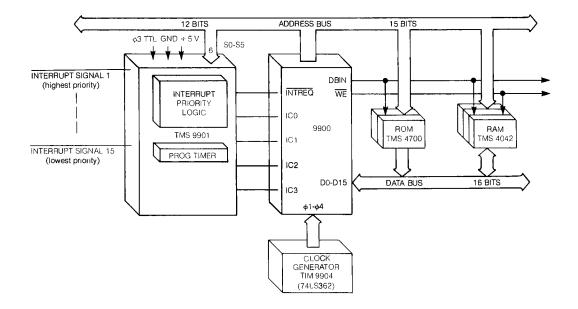

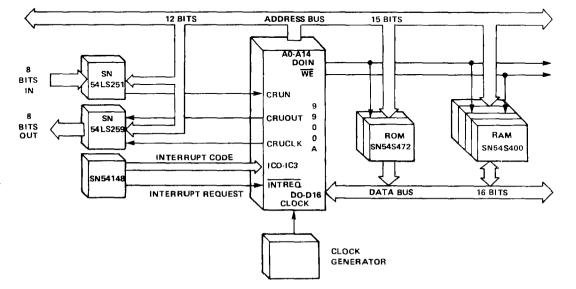

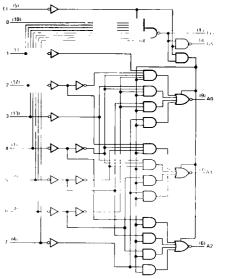

FIGURE 1 - ARCHITECTURE

▶8

8◄

FIGURE 2 - MEMORY MAP

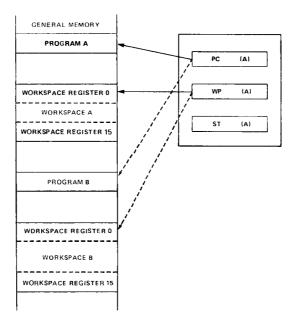

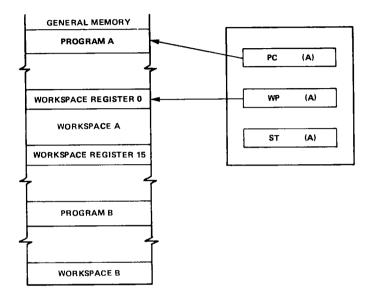

Three internal registers are accessible to the user. The program counter (PC) contains the address of the instruction following the current instruction being executed. This address is referenced by the processor to fetch the next instruction from memory and is then automatically incremented. The status register (ST) contains the present state of the processor and will be further defined in the Instruction Set section. The workspace pointer (WP) contains the address of the first word in the currently active set of workspace registers.

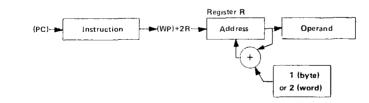

A workspace-register file occupies 16 contiguous memory words in the general memory area (see Figure 2). Each workspace register may hold data or addresses and function as operand registers, accumulators, address registers, or

index registers. During instruction execution, the processor addresses any register in the workspace by adding the register number to the contents of the workspace pointer and initiating a memory request for the word. The relationship between the workspace pointer and its corresponding workspace is shown below.

The workspace concept is particularly valuable during operations that require a context switch, which is a change from one program environment to another (as in the case of an interrupt) or to a subroutine. Such an operation, using a conventional multi-register arrangement, requires that at least part of the contents of the register file be stored and reloaded. A memory cycle is required to store or fetch each word. By exchanging the program counter, status register, and workspace pointer, the TMS 9900 accomplishes a complete context switch with only three store cycles and three fetch cycles. After the switch the workspace pointer contains the starting address of a new 16-word workspace in memory for use in the new routine. A corresponding time saving occurs when the original context is restored. Instructions in the TMS 9900 that result in a context switch include:

- 1. Branch and Load Workspace Pointer (BLWP)

- 2. Return from Subroutine (RTWP)

- 3. Extended Operation (XOP).

Device interrupts,  $\overrightarrow{\text{RESET}}$ , and  $\overrightarrow{\text{LOAD}}$  also cause a context switch by forcing the processor to trap to a service subroutine.

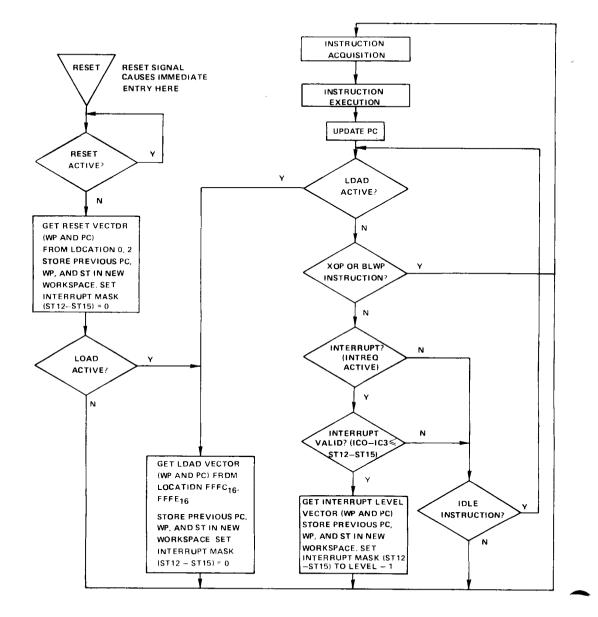

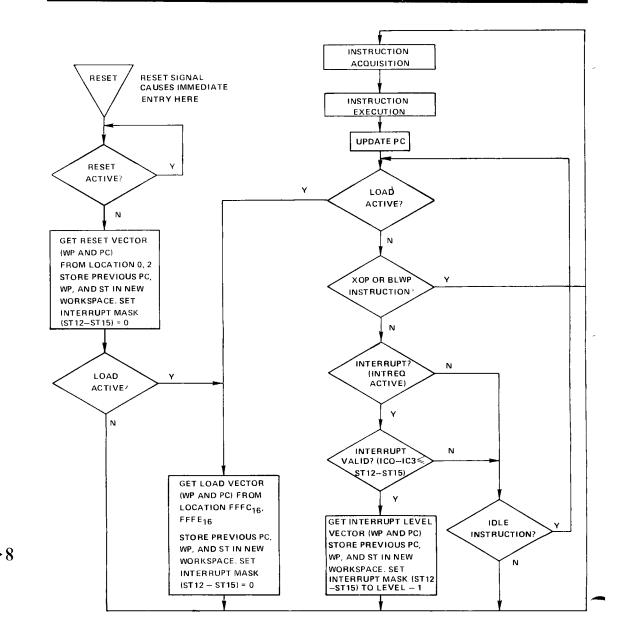

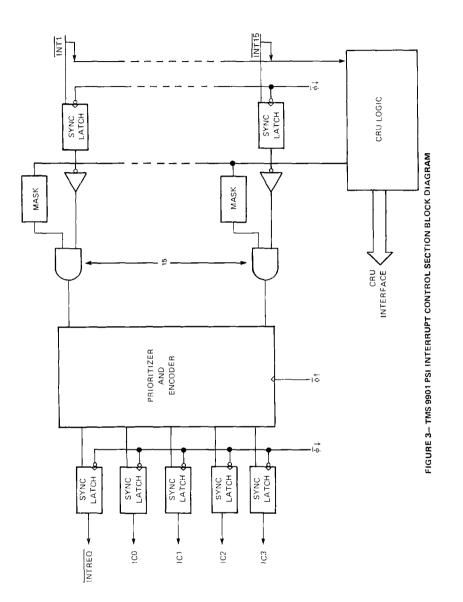

#### 2.2 INTERRUPTS

The <u>TMS 9900</u> employs 16 interrupt levels with the highest priority level 0 and lowest level 15. Level 0 is reserved for the <u>RESET</u> function and all other levels may be used for external devices. The external levels may also be shared by several device interrupts, depending upon system requirements.

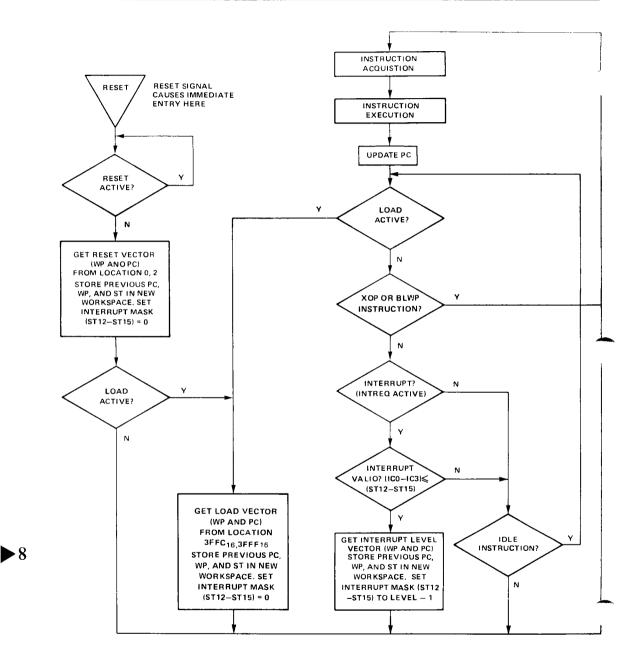

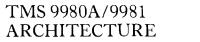

The TMS 9900 continuously compares the interrupt code (IC0 through IC3) with the interrupt mask contained in status-register bits 12 through 15. When the level of the pending interrupt is less than or equal to the enabling mask level (higher or equal priority interrupt), the processor recognizes the interrupt and initiates a context switch following

-8

completion of the currently executing instruction. The processor fetches the new context WP and PC from the interrupt vector locations. Then, the previous context WP, PC, and ST are stored in workspace registers 13, 14, and 15, respectively, of the new workspace. The TMS 9900 then forces the interrupt mask to a value that is one less than the level of the interrupt being serviced, except for level-zero interrupt, which loads zero into the mask. This allows only interrupts of higher priority to interrupt a service routine. The processor also inhibits interrupts until the first instruction of the service routine has been executed to preserve program linkage should a higher priority interrupt occur. All interrupt requests should remain active until recognized by the processor in the device-service routine. The individual service routines must reset the interrupt requests before the routine is complete.

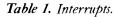

If a higher priority interrupt occurs, a second context switch occurs to service the higher priority interrupt. When that routine is complete, a return instruction (RTWP) restores the first service routine parameters to the processor to complete processing of the lower-priority interrupt. All interrupt subroutines should terminate with the return instruction to restore original program parameters. The interrupt-vector locations, device assignment, enabling-mask value, and the interrupt code are shown in Table 1.

|                      | Vector Location |                   | Interrupt Mask Values To     | Interrupt    |

|----------------------|-----------------|-------------------|------------------------------|--------------|

| Interrupt Level      | (Memory Address | Device Assignment | Enable Respective Interrupts | Codes        |

|                      | In Hex)         |                   | (ST12 thru ST15)             | IC0 thru IC3 |

| (Highest priority) 0 | 00              | Reset             | 0 through F*                 | 0000         |

| 1                    | 04              | External device   | 1 through F                  | 0001         |

| 2                    | 08              |                   | 2 through F                  | 0010         |

| 3                    | 0C              |                   | 3 through F                  | 0011         |

| 4                    | 10              |                   | 4 through F                  | 0100         |

| 5                    | 14              |                   | 5 through F                  | 0101         |

| 6                    | 18              |                   | 6 through F                  | 0110         |

| 7                    | 1C              |                   | 7 through F                  | 0111         |

| 8                    | 20              |                   | 8 through F                  | 1000         |

| 9                    | 24              |                   | 9 through F                  | 1001         |

| 10                   | 28              |                   | A through F                  | 1010         |

| 11                   | 2C              |                   | B through F                  | 1011         |

| 12                   | 30              |                   | C through F                  | 1100         |

| 13                   | 34              |                   | D through F                  | 1101         |

| 14                   | 38              | ↓ ★               | E and F                      | 1110         |

| (Lowest priority) 15 | 3C              | External device   | Foniy                        | \$111        |

TABLE 1 INTERRUPT LEVEL DATA

\*Level 0 can not be disabled.

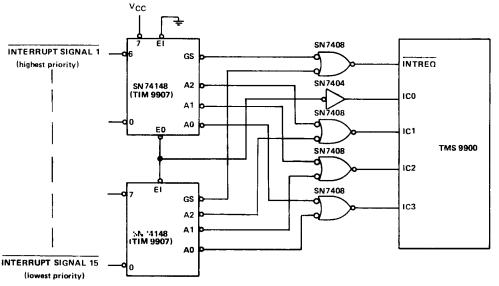

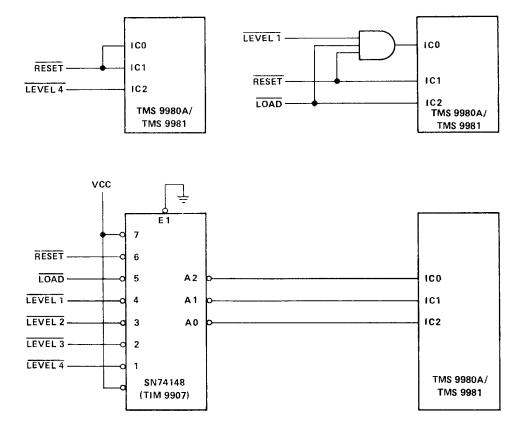

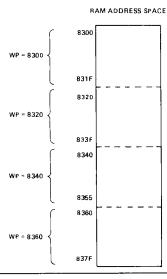

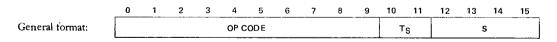

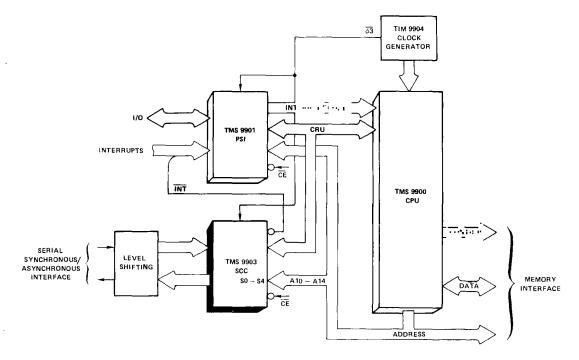

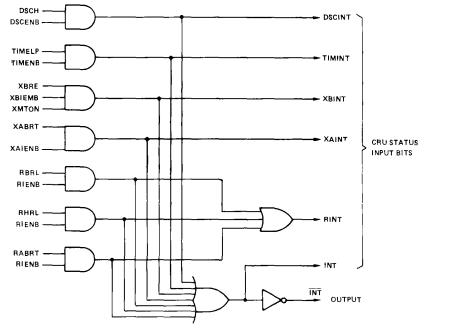

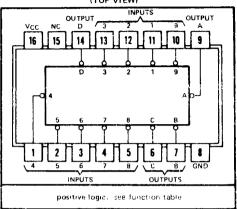

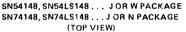

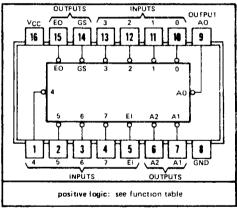

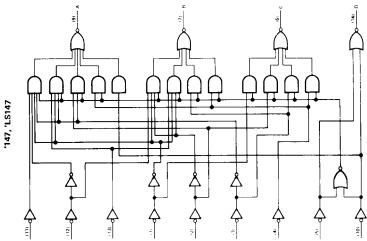

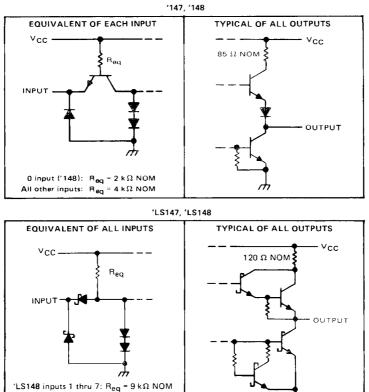

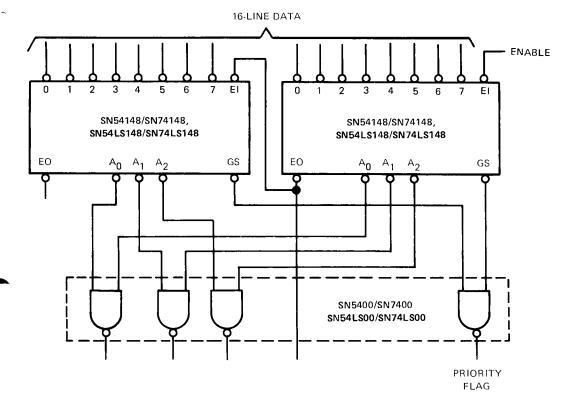

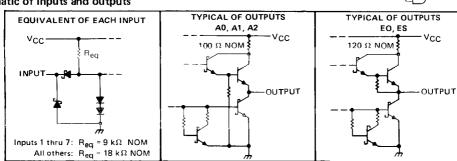

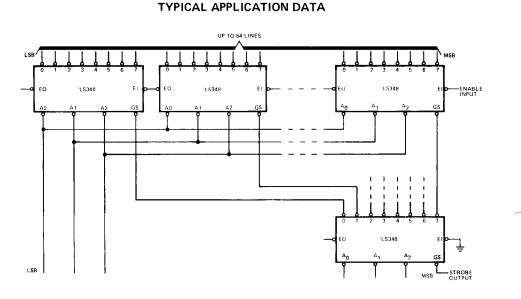

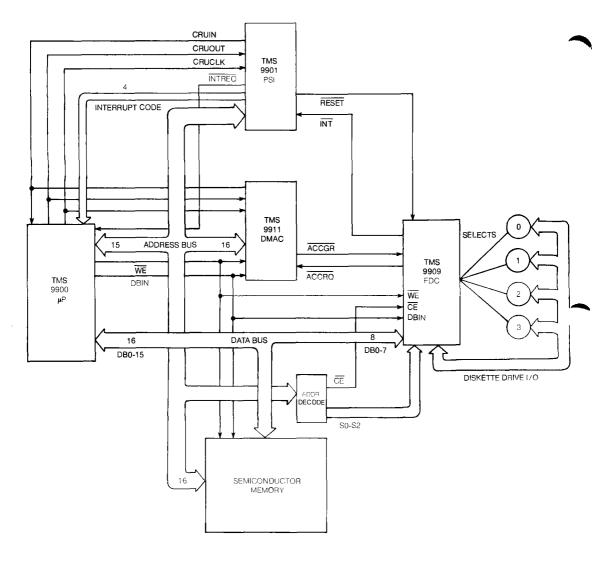

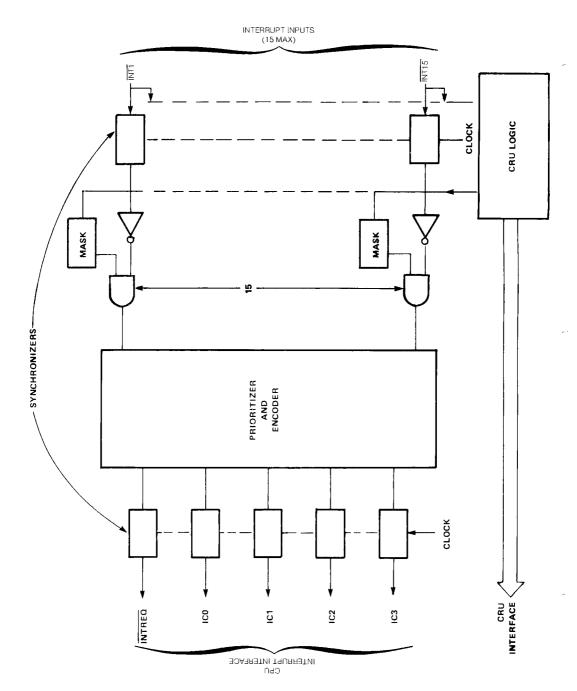

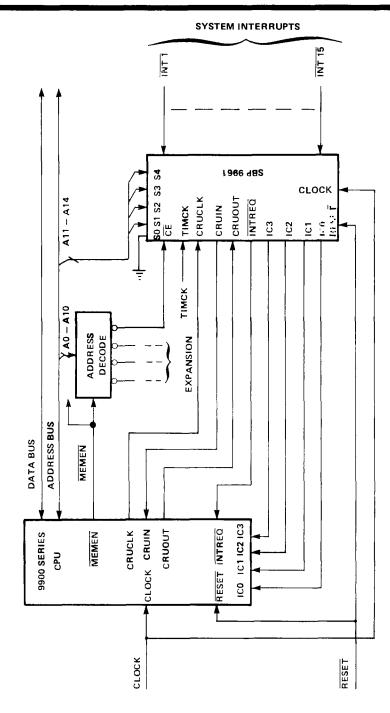

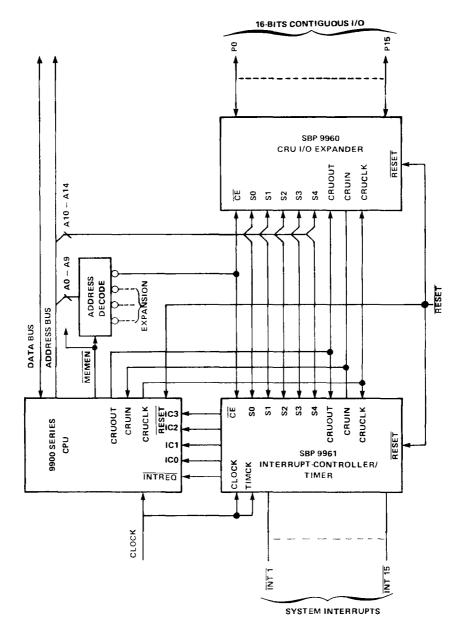

The TMS 9900 interrupt interface utilizes standard TTL components as shown in F  $\dots$  3. Note that for eight or less external interrupts a single SN74148 is required and for one external interrupt  $\overline{\text{INT}}$  is used as the interrupt signal with a hard-wired code IC0 through IC3.

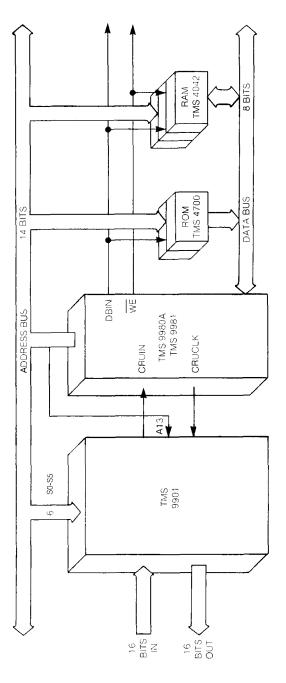

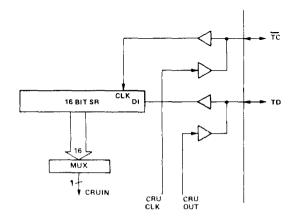

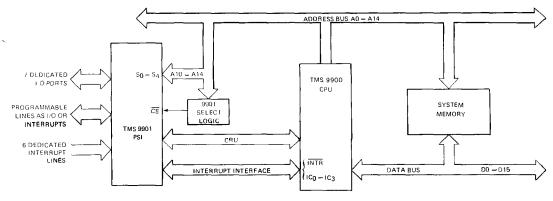

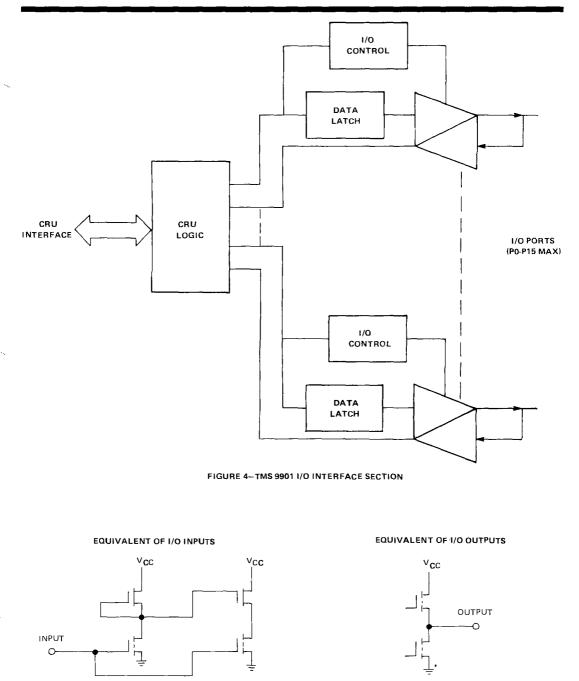

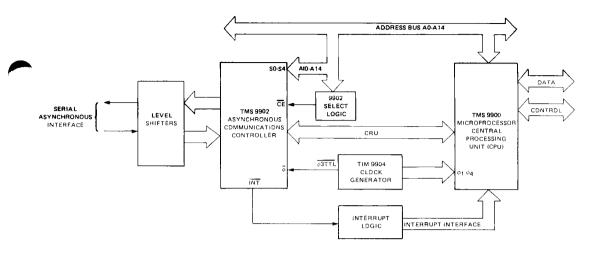

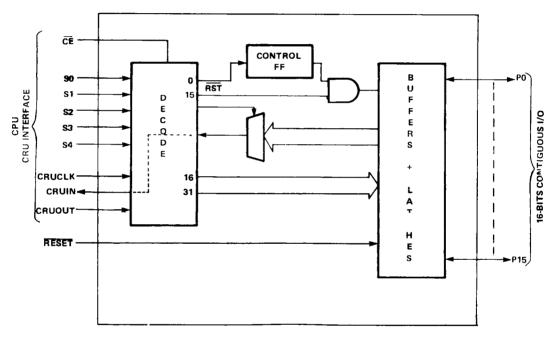

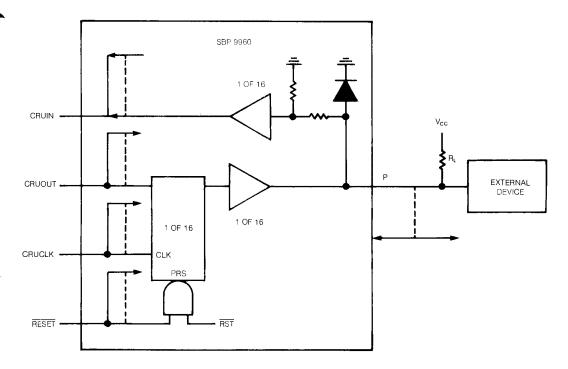

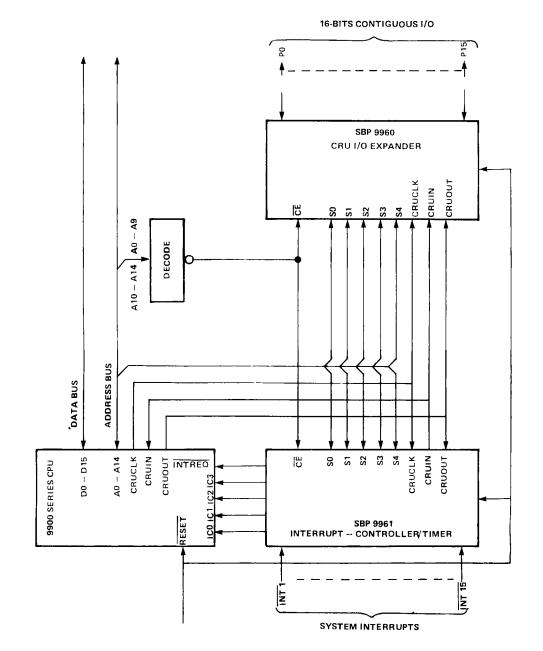

#### 2.3 INPUT/OUTPUT

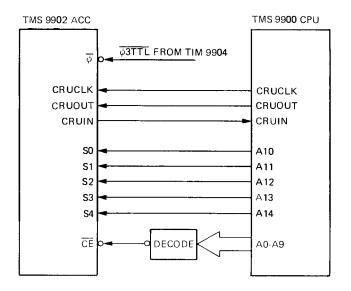

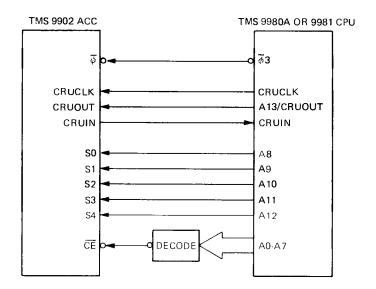

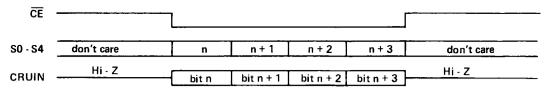

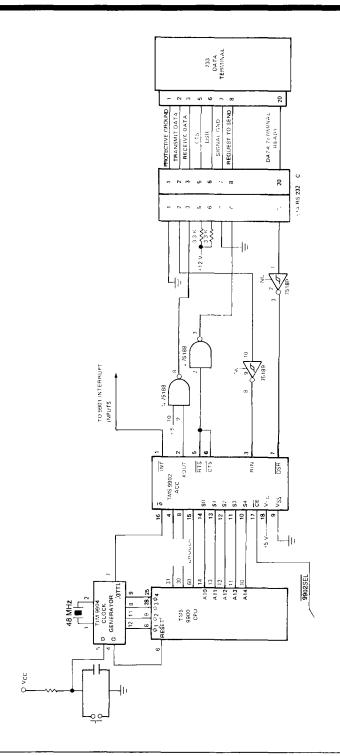

The TMS 9900 utilizes a versatile direct command-driven I/O interface designated as the communications-register unit (CRU). The CRU provides up to 4096 directly addressable input bits and 4096 directly addressable output bits. Both input and output bits can be addressed individually or in fields of from 1 to 16 bits. The TMS 9900 employs three dedicated I/O pins (CRUIN, CRUOUT, and CRUCLK) and 12 bits (A3 through A14) of the address bus to interface with the CRU system. The processor instructions that drive the CRU interface can set, reset, or test any bit in the CRU array or move between memory and CRU data fields.

FIGURE 3 - TMS 9900 INTERRUPT INTERFACE

#### 2.4 SINGLE-BIT CRU OPERATIONS

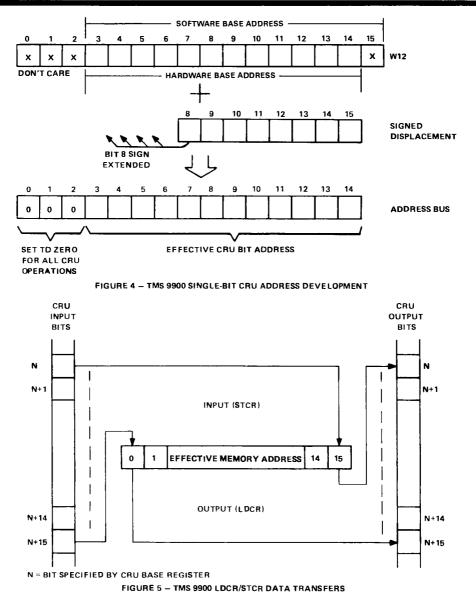

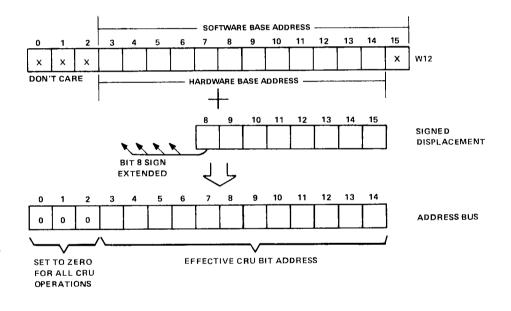

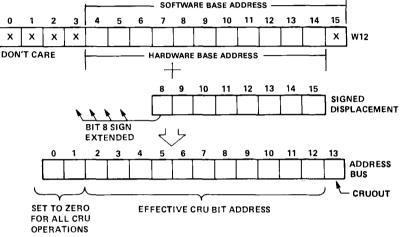

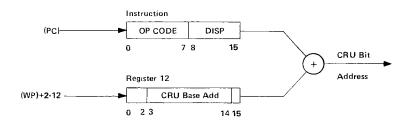

The TMS 9900 performs three single-bit CRU functions: test bit (TB), set bit to one (SBO), and set bit to zero (SBZ) To identify the bit to be operated upon, the TMS 9900 develops a CRU-bit address and places it on the address bus, A3 to A14.

For the two output operations (SBO and SBZ), the processor also generates a CRUCLK pulse, indicating an output operation to the CRU device, and places bit 7 of the instruction word on the CRUOUT line to accomplish the specified operation (bit 7 is a one for SBO and a zero for SBZ). A test-bit instruction transfers the addressed CRU bit from the CRUIN input line to bit 2 of the status register (EQUAL).

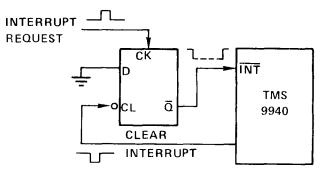

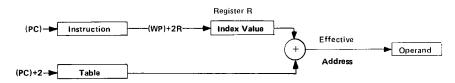

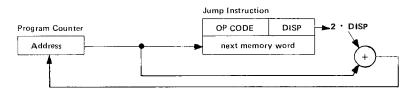

The TMS 9900 develops a CRU-bit address for the single-bit operations from the software base address contained in workspace register 12 and the signed displacement count contained in bits 8 through 15 of the instruction. The displacement allows two's complement addressing from base minus 128 bits through base plus 127 bits. The hardware base address, bits 3 through 14 of W12, is added to the signed displacement specified in the instruction and the result is loaded onto the address bus. *Figure 4* illustrates the development of a single-bit CRU address.

#### 2.5 MULTIPLE-BIT CRU OPERATIONS

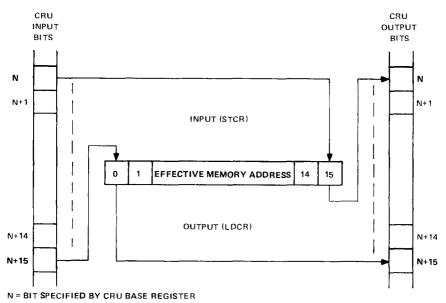

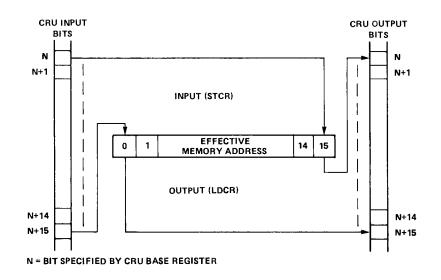

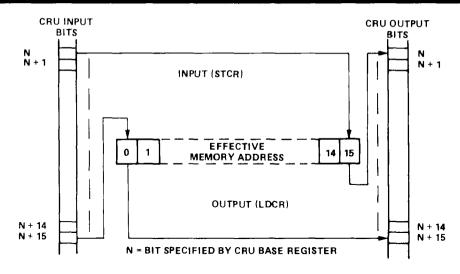

The TMS 9900 performs two multiple-bit CRU operations: store communications register (STCR) and load communications register (LDCR). Both operations perform a data transfer from the CRU-to-memory or from memory-to-CRU as illustrated in Figure 5. Although the figure illustrates a full 16-bit transfer operation, any number of bits from 1 through 16 may be involved. The LDCR instruction fetches a word from memory and right-shifts it to-serially transfer it to CRU output bits. If the LDCR involves eight or fewer bits, those bits come from the right-justified field within the addressed byte of the memory word. If the LDCR involves nine or more bits, those bits come from the right-justified field within the whole memory word. When transferred to the CRU interface, each successive bit receives an address that is sequentially greater than the address for the previous bit. This addressing mechanism results in an order reversal of the bits; that is, bit 15 of the memory word (or bit 7) becomes the lowest addressed bit in the CRU and bit 0 becomes the highest addressed bit in the CRU field.

An STCR instruction transfers data from the CRU to memory. If the operation involves a byte or less transfer, the transferred data will be stored right-justified in the memory byte with leading bits set to zero. If the operation involves from nine to 16 bits, the transferred data is stored right-justified in the memory word with leading bits set to zero.

When the input from the CRU device is complete, the first bit from the CRU is the least-significant-bit position in the memory word or byte.

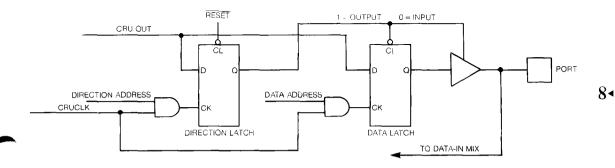

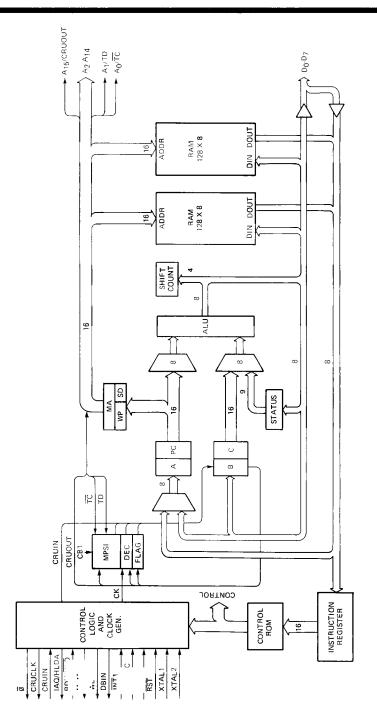

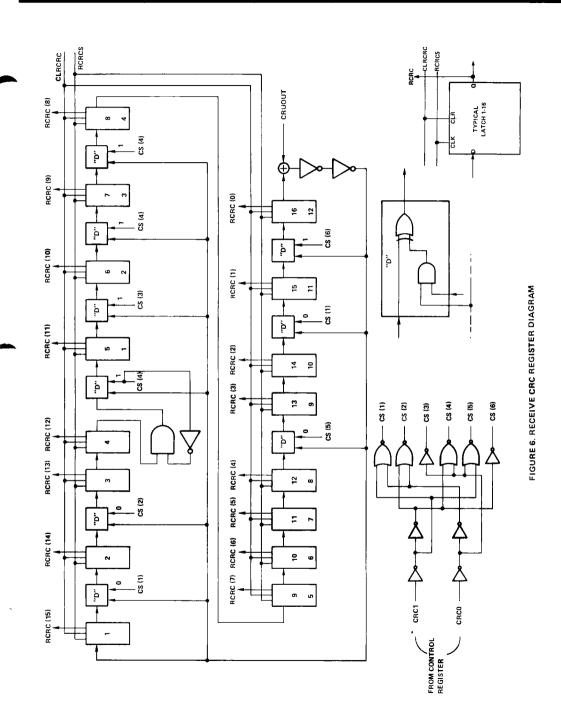

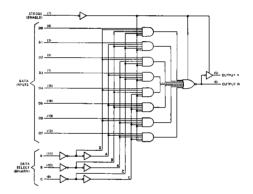

Figure 6 illustrates how to implement a 16-bit input and a 16-bit output register in the CRU interface. CRU addresses are decoded as needed to implement up to 256 such 16-bit interface registers. In system application, however, only the exact number of interface bits needed to interface specific peripheral devices are implemented. It is not necessary to have a 16-bit interface register to interface an 8-bit device.

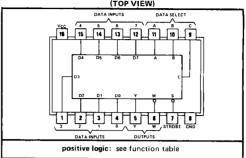

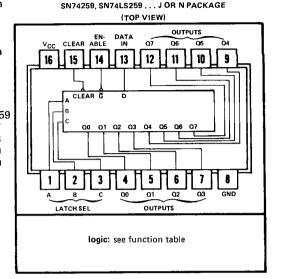

FIGURE 6 - TMS 9900 16-BIT INPUT/OUTPUT INTERFACE

#### 2.6 EXTERNAL INSTRUCTIONS

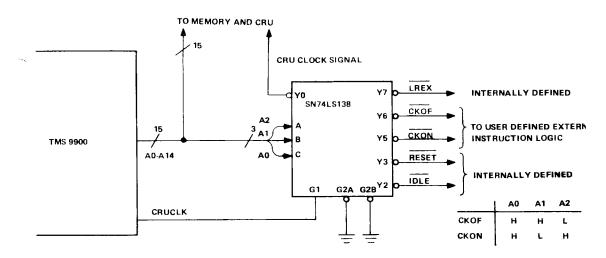

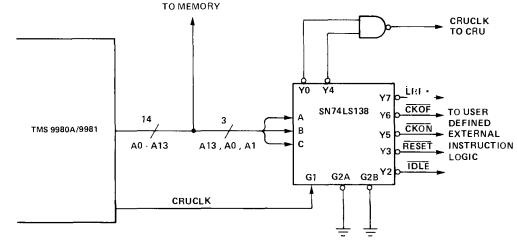

The TMS 9900 has five external instructions that allow user-defined external functions to be initiated under program control. These instructions are CKON, CKOF, RSET, IDLE, and LREX. These mnemonics, except for IDLE, relate to functions implemented in the 990 minicomputer and do not restrict use of the instructions to initiate various user-defined functions. IDLE also causes the TMS 9900 to enter the idle state and remain until an interrupt, RESET, or LOAD occurs. When any of these five instructions are executed by the TMS 9900, a unique 3-bit code appears on the most-significant 3 bits of the address bus (A0 through A2) along with a CRUCLK pulse. When the TMS 9900 is in an idle state, the 3-bit code and CRUCLK pulses occur repeatedly until the idle state is terminated. The codes are:

| EXTERNAL INSTRUCTION | A0 | A1 | AZ |

|----------------------|----|----|----|

| LREX                 | н  | н  | н  |

| CKOF                 | н  | н  | L  |

| CKON                 | н  | L  | н  |

| RSET                 | L  | н  | н  |

| IOLE                 | L  | н  | Ł  |

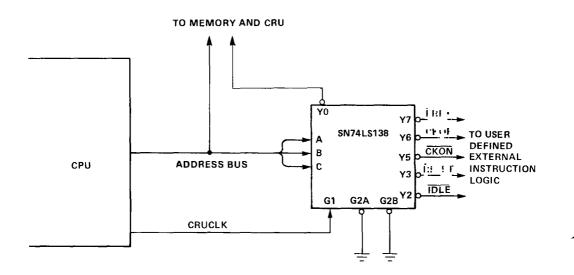

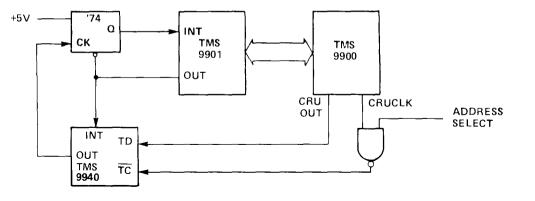

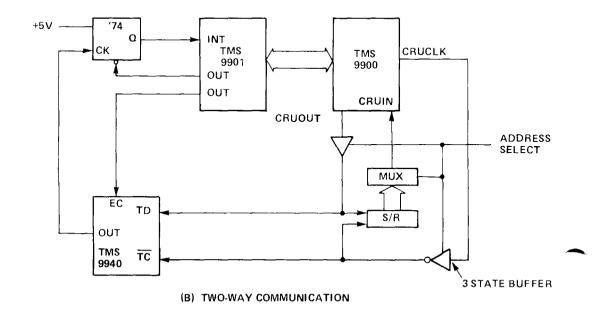

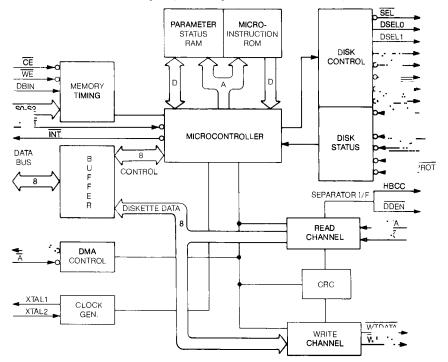

Figure 7 illustrates typical external decode logic to implement these instructions. Note that a signal is generated to inhibit CRU decodes during external instructions.

FIGURE 7 - EXTERNAL INSTRUCTION DECODE LOGIC

#### 2.7 LOAD FUNCTION

The LOAD signal allows cold-start ROM loaders and front panels to be implemented for the TMS 9900. When active, LOAD causes the TMS 9900 to initiate an interrupt sequence immediately following the instruction being executed. Memory location FFFC is used to obtain the vector (WP and PC). The old PC, WP and ST are loaded into the new workspace and the interrupt mask is set to 0000. Then, program execution resumes using the new PC and WP.

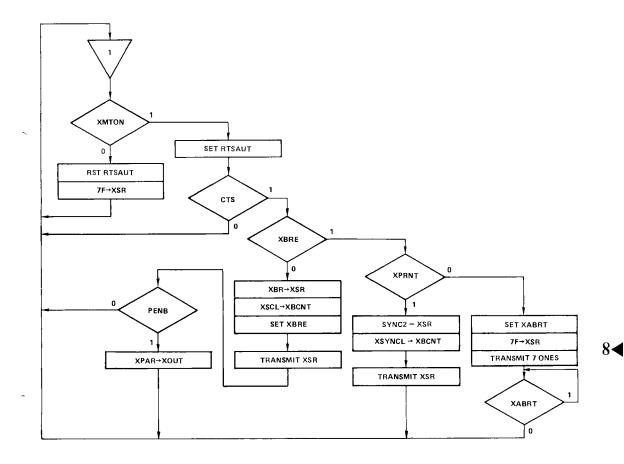

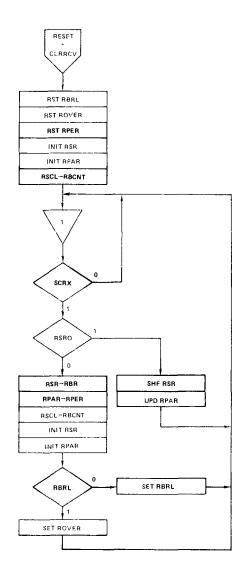

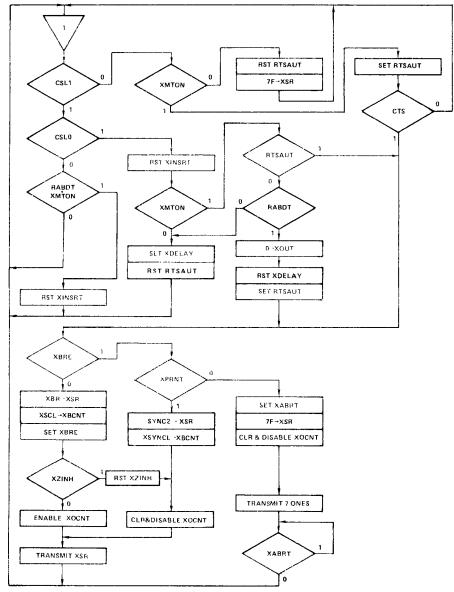

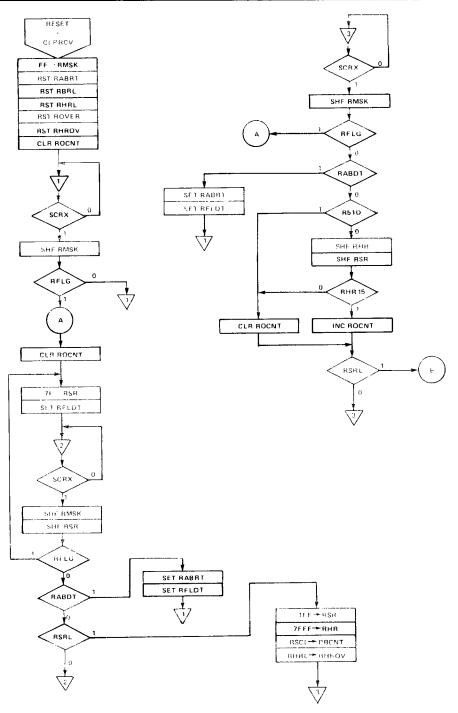

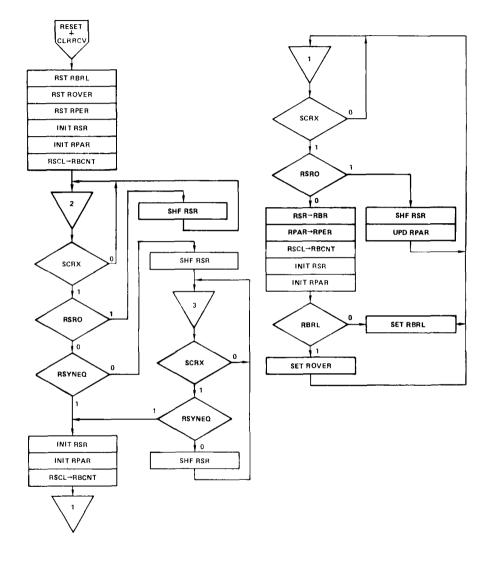

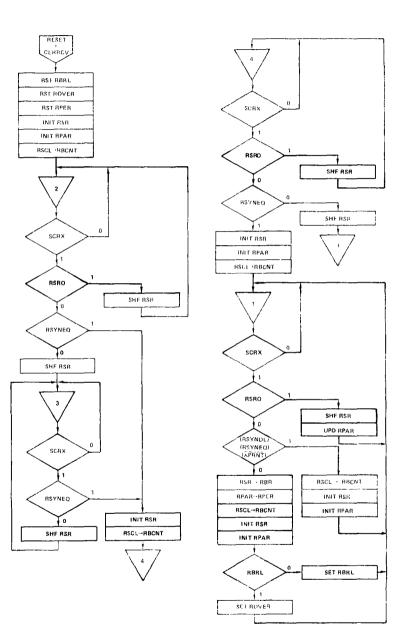

#### FIGURE 8 - TMS 9900 CPU FLOW CHART

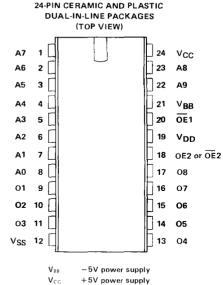

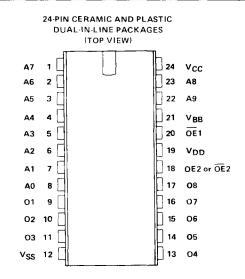

#### 2.8 TMS 9900 PIN DESCRIPTION

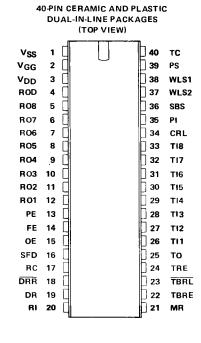

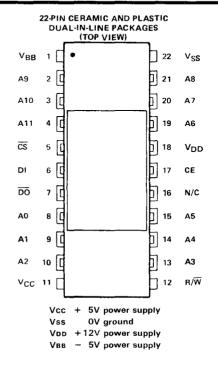

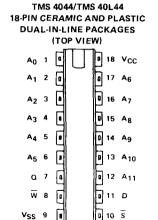

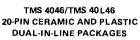

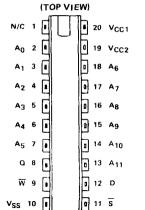

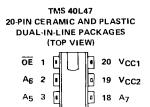

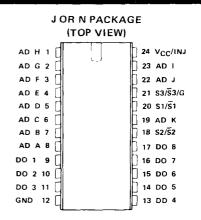

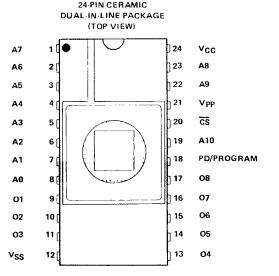

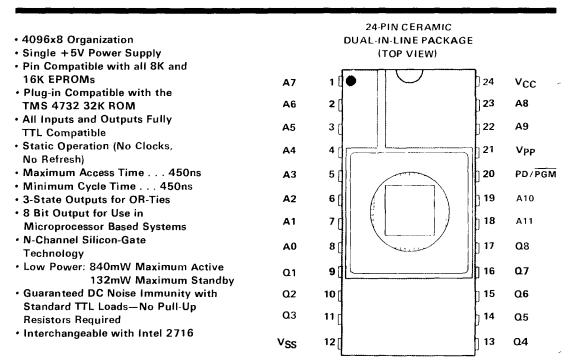

Table 2 defines the TMS 9900 pin assignments and describes the function of each pin.

# TABLE 2 TMS 9900 PIN ASSIGNMENTS AND FUNCTIONS

| SIGNATURE       | PIN      | 1/0 | DESCRIPTION                                  |                 | TMS          | 9900 PIN ASSIGNMENTS              |    |

|-----------------|----------|-----|----------------------------------------------|-----------------|--------------|-----------------------------------|----|

|                 |          |     | ADD RESS BUS                                 | ∨ <sub>BB</sub> | 1 ස්ට්       | 64 HOLD                           |    |

| A0 (MSB)        | 24       | ουτ | A0 through A14 comprise the address bus.     | V <sub>CC</sub> | 2            | 0 63 MEME                         | Ň  |

| A1              | 23       | ουτ | This 3-state bus provides the memory-        | WAIT            | 3            | CI 62 READ                        | 1  |

| A2              | 22       | ουτ | advdress vector to the external-memory       | LOAD            | 4 6          | ⊂,161 WE                          |    |

| A3              | 21       | ουτ | system when MEMEN is active and I/O-bit      | HOLDA           | 5 🖒          |                                   | .к |

| A4              | 20       | ουτ | addresses and external-instruction addresses | RESET           | 6 対          | L‡\$59 V <sub>CC</sub>            |    |

| A5              | 19       | ουτ | to the I/O system when MEMEN is inactive.    | IAQ             | 76           | 58 NC                             |    |

| A6              | 18       | Ουτ | The address bus assumes the high-impedance   | φ1              | 8 🖒          | 157 NC                            |    |

| A7              | 17       | Ουτ | state when HOLDA is active.                  | φ2              | 9 📫          | <b>⊑</b> ‡156 D15                 |    |

| A8              | 16       | δυτ |                                              | A14             | 10 岸         | C155 D14                          |    |

| A9              | 15       | Ουτ |                                              | A13             | 11 🛱         | 🗖 🛱 54 D13                        |    |

| A10             | 14       | ουτ |                                              | A12             | I            | □ <b>53</b> D12                   |    |

| A11             | 13       | OUT |                                              | A11             | 13 🖾         | □ <b>52</b> D11                   |    |

| A12             | 12       | OUT |                                              | A10             | 14 🟳         | F <sup>1</sup> 51 D10             |    |

| A13             | 11       | Ουτ |                                              | A9              | 15 🛱         | <b>50 D9</b>                      |    |

| A14 (LSB)       | 10       | OUT |                                              | A8              | 16 🟳         | <b>49 D8</b>                      |    |

|                 |          |     |                                              | A7              | - T.         | <b>148</b> D7                     |    |

|                 |          |     | DATA BUS                                     | A6              |              |                                   |    |

| DO (MSB)        | 41       | 1/0 | D0 through D15 comprise the bidirectional    | A5              | ···•         |                                   |    |

| D1              | 42       | 1/0 | 3-state data bus. This bus transfers memory  |                 | 20 57        |                                   |    |

| D2              | 43       | 1/0 | data to (when writing) and from (when        |                 | 21           |                                   |    |

| D3              | 44       | 1/0 | reading) the external-memory system when     |                 | 21           | □ 1 43 D2<br>□ 1 42 D1            |    |

| D4              | 45<br>46 | 1/0 | MEMEN is active. The data bus assumes the    |                 | 23 K<br>24 K |                                   |    |

| D5<br>D6        | 40       | 1/0 | high-impedance state when HOLDA is active.   |                 |              |                                   |    |

| D6<br>D7        | 47       | 1/0 | active.                                      |                 | 26           | □ 140 V <sub>SS</sub><br>□ 139 NC |    |

|                 | 49       | 1/D |                                              | vss<br>VDD      | 1            |                                   |    |

| D8<br>D9        | 50       | 1/0 |                                              |                 | 28           |                                   |    |

| D10             | 51       | 1/D |                                              | ψ3<br>DBIN      |              |                                   |    |

| D11             | 52       | 1/0 |                                              | CRUOUT          | 1            |                                   |    |

| D12             | 53       | 1/D |                                              | CRUIN           |              |                                   |    |

| D13             | 54       | 1/0 |                                              | INTRED          |              |                                   |    |

| D14             | 55       | 1/D |                                              | in the c        | E            |                                   |    |

| D15 (LSB)       | 56       | 1/D |                                              |                 |              |                                   |    |

| 010 (200)       |          |     |                                              | NC – No Ir      | tarnal co    | opaction                          |    |

|                 |          |     | POWER SUPPLIES                               |                 |              | nnachon                           |    |

| ∨ <sub>BB</sub> | 1        |     | Supply voltage (-5 V NOM)                    |                 |              |                                   |    |

| Vcc             | 2,59     |     | Supply voltage (5 V NOM), Pins 2 and 59 n    | nust be con     | nected in    | parallel.                         |    |

| VDD             | 27       |     | Supply voltage (12 V NOM)                    |                 |              |                                   |    |

| ∨ <sub>SS</sub> | 26,40    |     | Ground reference, Pins 26 and 40 must be o   | connected i     | n paraliel,  |                                   |    |

|                 | 1        |     |                                              |                 |              |                                   |    |

|                 |          |     | CLOCKS                                       |                 |              |                                   |    |

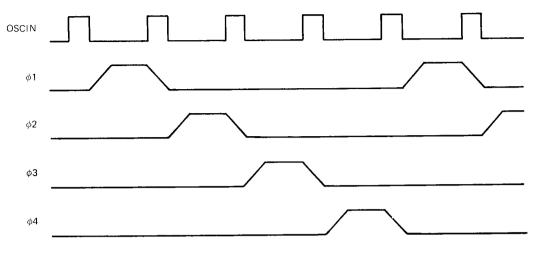

| φ1              | 8        | IN  | Phase-1 clock                                |                 |              |                                   |    |

| φ2              | 9        | IN  | Phase-2 clock                                |                 |              |                                   |    |

| φ3              | 28       | IN  | Phase-3 clock                                |                 |              |                                   |    |

| φ <b>4</b>      | 25       | IN  | Phase-4 clock                                |                 |              |                                   |    |

|                 |          |     |                                              |                 |              |                                   |    |

|                                      |                      |                | TABLE 2 (CONTINUED)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|--------------------------------------|----------------------|----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| SIGNATURE                            | PIN                  | ١/٥            | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| DBIN                                 | 29                   | Ουτ            | BUS CONTROL<br>Data bus in. When active (high), DBIN indicates that the TMS 9900 has disabled its output buffers to<br>allow the memory to place memory-read data on the data bus during MEMEN. DBIN remains low in<br>all other cases except when HOLDA is active.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| MEMEN                                | 63                   | ουτ            | Memory enable. When active (low), MEMEN indicates that the address bus contains a memory address.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| WE                                   | 61                   | оυт            | Write enable. When active (low), WE indicates that memory-write data is available from the TMS 9900 to be written into memory.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| CRUCLK                               | 60                   | ουτ            | CRU clock. When active (high), CRUCLK indicates that external interface logic should sample the<br>output data on CRUOUT or should decode external instructions on A0 through A2.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| CRUIN                                | 31                   | IN             | CRU data in. CRUIN, normally driven by 3-state or open-collector devices, receives input data from external interface logic. When the processor executes a STCR or TB instruction, it samples CRUIN for the level of the CRU input bit specified by the address bus (A3 through A14).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| CRUOUT                               | 30                   | ОUТ            | CRU data out. Serial I/O data appears on the CRUOUT line when an LDCR, SBZ, or SBO instruction is executed. The data on CRUOUT should be sampled by external I/O interface logic when CRUCLK goes active (high).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| INTREQ                               | 32                   | IN             | INTERRUPT CONTROL<br>Interrupt request. When active (low), INTREQ indicates that an external interrupt is requested. If<br>INTREQ is active, the processor loads the data on the interrupt-code-input lines ICO through IC3 into<br>the internal interrupt-code-storage register. The code is compared to the interrupt mask bits of the<br>status register. If equal or higher priority than the enabled interrupt level (interrupt code equal or less<br>than status register bits 12 through 15) the TMS 9900 interrupt sequence is initiated. If the<br>comparison fails, the processor ignores the request. INTREQ should remain active and the processor<br>will continue to sample ICO through IC3 until the program enables a sufficiently low priority to accept<br>the request interrupt. |

| ICO (MSB)<br>IC1<br>IC2<br>IC3 (LSB) | 36<br>35<br>34<br>33 | IN<br>IN<br>IN | Interrupt codes. ICO is the MSB of the interrupt code, which is sampled when INTREQ is active. When ICO through ICO are LLLH, the highest external-priority interrupt is being requested and when HHHH, the lowest-priority interrupt is being requested.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| + HOLD                               | 64                   | IN             | $\label{eq:memory} \begin{array}{c} \textbf{MEMORY CONTROL} \\ \mbox{Hold. When active (low), $\overline{HOLD}$ indicates to the processor that an external controller (e.g., DMA device) desires to utilize the address and data buses to transfer data to or from memory. The TMS 9900 enters the hold state following a hold signal when it has completed its present memory cycle.* The processor then places the address and data buses in the high-impedance state (along with $WE, $MEMEN,$ and DBIN) and responds with a hold-acknowledge signal (HOLDA). When $HOLD$ is removed, the processor returns to normal operation. \\ \end{array}$                                                                                                                                                |

| HOLDA                                | 5                    | оит            | Hold acknowledge. When active (high), HOLDA indicates that the processor is in the hold state and the address and data buses and memory control outputs (WE, MEMEN, and DBIN) are in the high-impedance state.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| READY                                | 62                   | IN             | Ready. When active (high), READY indicates that memory will be ready to read or write during the<br>next clock cycle. When not-ready is indicated during a memory operation, the TMS 9900 enters a wait<br>state and suspends internal operation until the memory systems indicate ready.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| WAIT                                 | 3                    | ουτ            | Wait. When active (high), WAIT indicates that the TMS 9900 has entered a wait state because of a not-ready condition from memory.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|                                      |                      |                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

If the cycle following the present memory cycle is also a memory cycle, it, too, is completed before the TMS9900 enters the hold state. The maximum number of consecutive memory cycles is three.

7

▶8

#### TABLE 2 (CONCLUDED)

| SIGNATURE | PIN | 1/0 | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|-----------|-----|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| DAI       | 7   | OUT | TIMING AND CONTROL<br>Instruction acquisition. IAQ is active (high) during any memory cycle when the TMS 9900 is acquiring an<br>instruction. IAQ can be used to detect illegal op codes.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| LOAD      | 4   | IN  | Load. When active (low), LOAD causes the TMS 9900 to execute a nonmaskable interrupt with memory address FFFC16 containing the trap vector (WP and PC). The load sequence begins after the instruction being executed is completed. LOAD will also terminate an idle state. If LOAD is active during the time RESET is released, then the LOAD trap will occur after the RESET function is completed. LOAD should remain active for one instruction period. IAQ can be used to determine instruction boundaries. This signal can be used to implement cold-start ROM loaders. Additionally, front-panel routines can be implemented using CRU bits as front-panel-interface signals and software-control routines to control the panel operations. |

| RESET     | 6   | IN  | Reset. When active (low), RESET causes the processor to be reset and inhibits WE and CRUCLK. When RESET is released, the TMS 9900 then initiates a level-zero interrupt sequence that acquires WP and PC from locations 0000 and 0002, sets all status register bits to zero, and starts execution. RESET will also terminate an idle state. RESET must be held active for a minimum of three clock cycles.                                                                                                                                                                                                                                                                                                                                        |

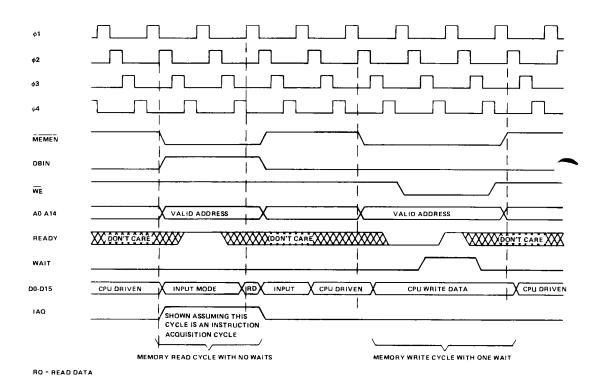

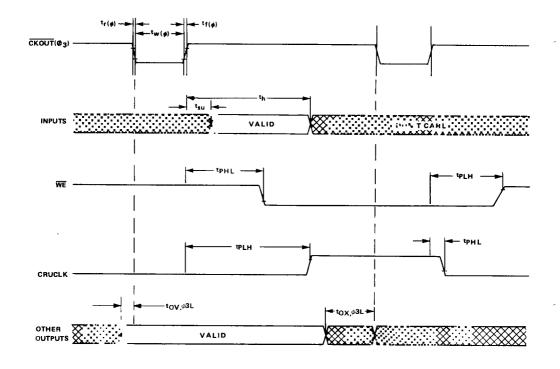

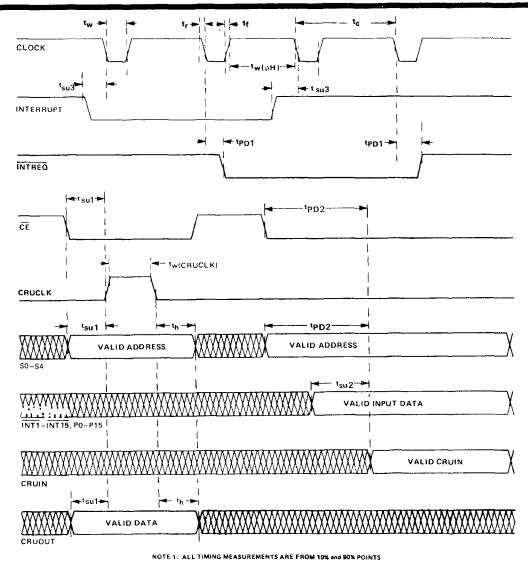

#### 2.9 T)MING

#### 2.9.1 MEMORY

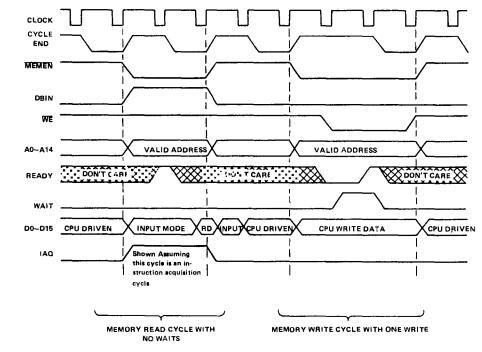

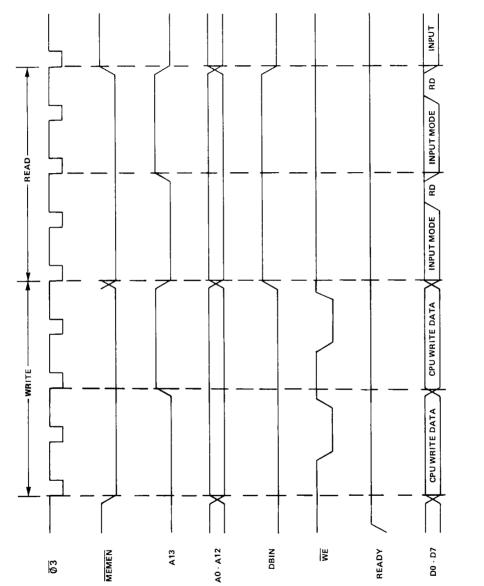

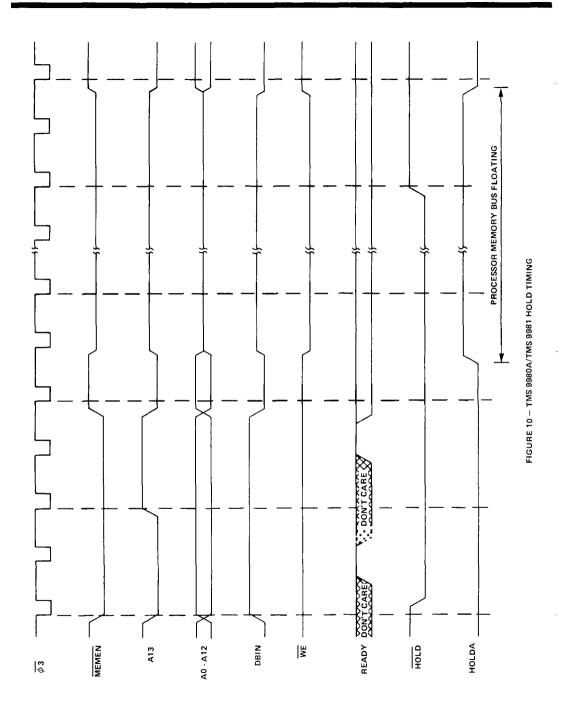

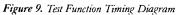

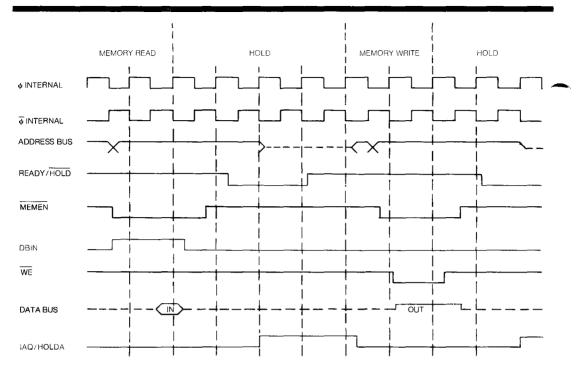

A basic memory read and write cycle is shown in Figure 9. The read cycle is shown with no wait states and the write cycle is shown with one wait state.

**MEMEN** goes active (low) during each memory cycle. At the same time that **MEMEN** is active, the memory address appears on the address bus bits A0 through A14. If the cycle is a memory-read cycle, DBIN will go active (high) at the same time **MEMEN** and A0 through A14 become valid. The memory-write signal **WE** will remain inactive (high) during a read cycle. If the read cycle is also an instruction acquisition cycle, IAQ will go active (high) during the cycle.

The READY signal, which allows extended memory cycles, is shown high during  $\phi$ 1-of the second clock cycle of the read operation. This indicates to the TMS 9900 that memory-read data will be valid during  $\phi$ 1 of the next clock cycle. If READY is low during  $\phi$ 1, then the TMS 9900 enters a wait state suspending internal operation until a READY is sensed during a subsequent  $\phi$ 1. The memory read data is then sampled by the TMS 9900 during the next  $\phi$ 1, which completes the memory-read cycle.

At the end of the read cycle, MEMEN and DBIN go inactive (high and low, respectively). The address bus may also change at this time, however, the data bus remains in the input mode for one clock cycle after the read cycle.

A write cycle is similar to the read cycle with the exception that  $\overline{WE}$  goes active (low) as shown and valid write data appears on the data bus at the same time the address appears. The write cycle is shown as an example of a one-wait-state memory cycle. READY is low during  $\phi$ 1 resulting in the WAIT signal shown.

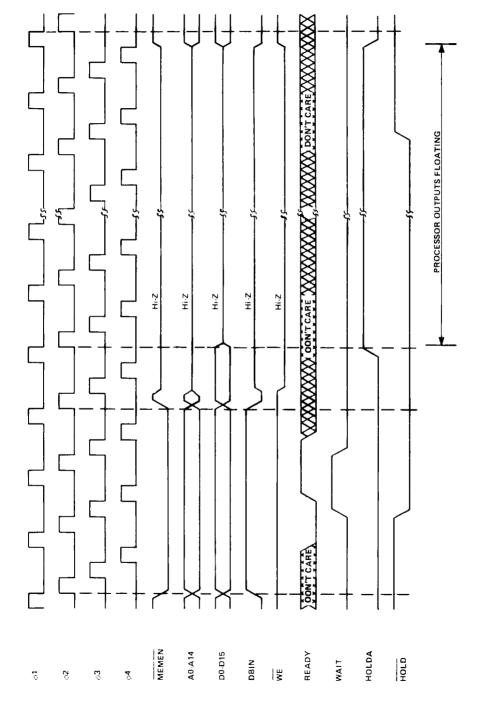

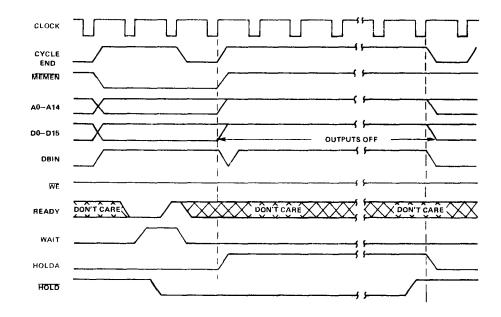

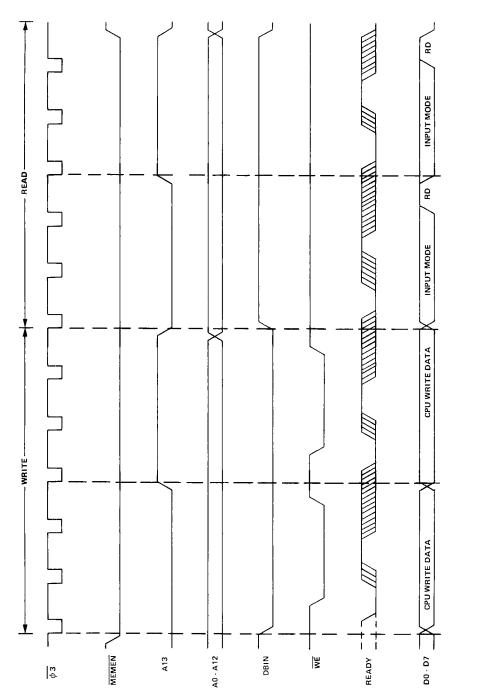

#### 2.9.2 HOLD

Other interfaces may utilize the TMS 9900 memory bus by using the hold operation (illustrated in Figure 10) of the TMS 9900. When HOLD is active (low), the TMS 9900 enters the hold state at the next available non-memory cycle. Considering that there can be a maximum of three consecutive memory cycles, the maximum delay between HOLD going active to HOLDA going active (high) could be  $t_{C(\phi)}$  (for setup) + (6 + 3W)  $t_{C(\phi)}$  +  $t_{C(\phi)}$  (delay for HOLDA), where W is the number of wait states per memory cycle and  $t_{C(\phi)}$  is the clock cycle time. When the TMS 9900 has entered the hold state, HOLDA goes active (high) and A0 through A15, D0 through D15 DBIN, MEMEN, and WE go into a high-impedance state to allow other devices to use the memory buses. When HOLD goes inactive (high), the TMS 9900 resumes processing as shown. If hold occurs during a CRU operation, the TMS 9900 uses an extra clock cycle (after the removal of the HOLD signal) to reassert the CRU address providing the normal setup times for the CRU bit transfer that was interrupted.

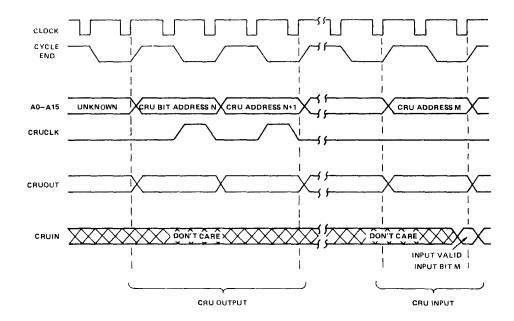

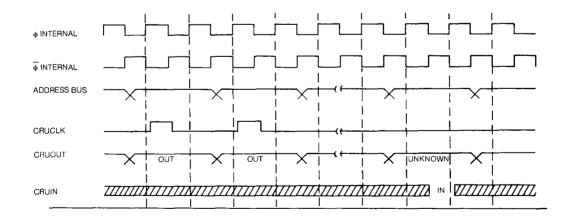

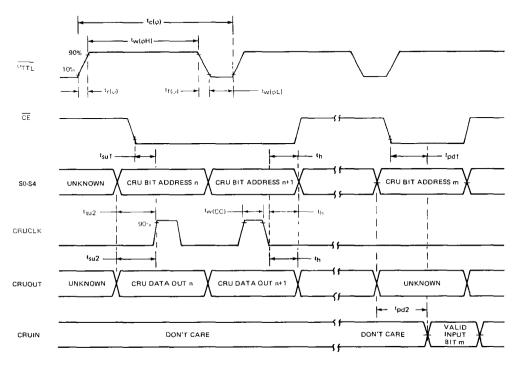

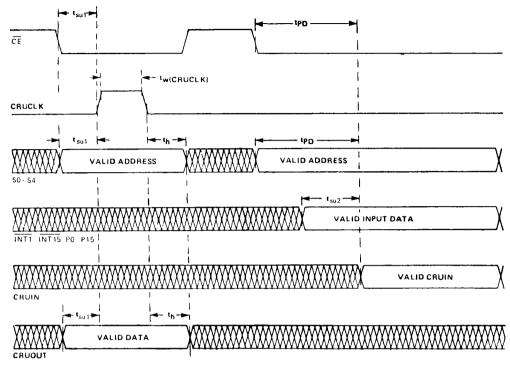

#### 2.9.3 CRU

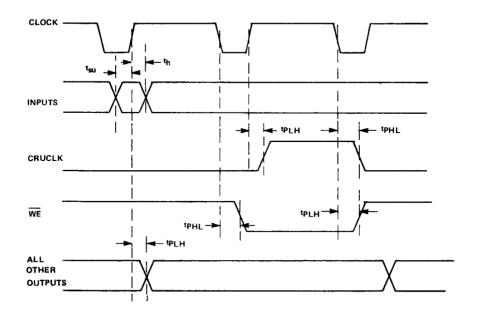

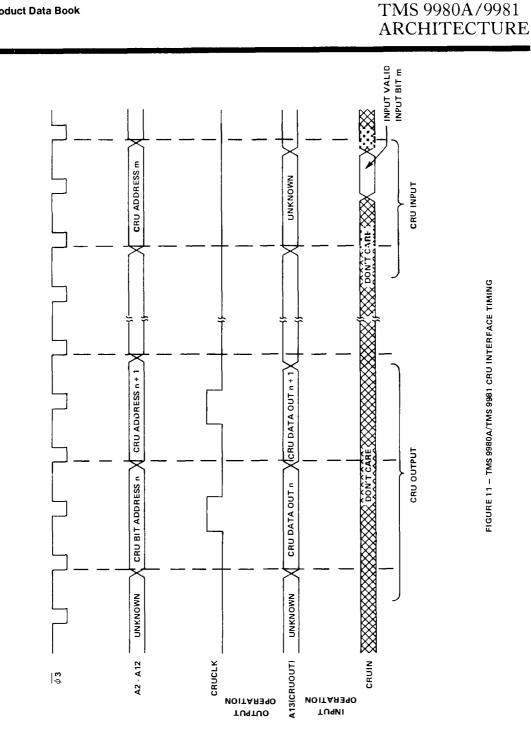

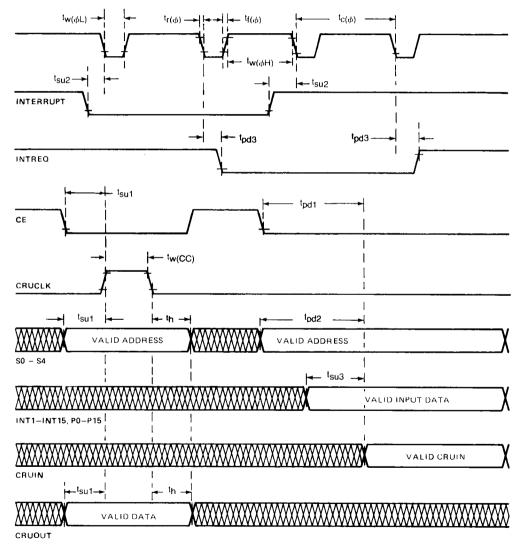

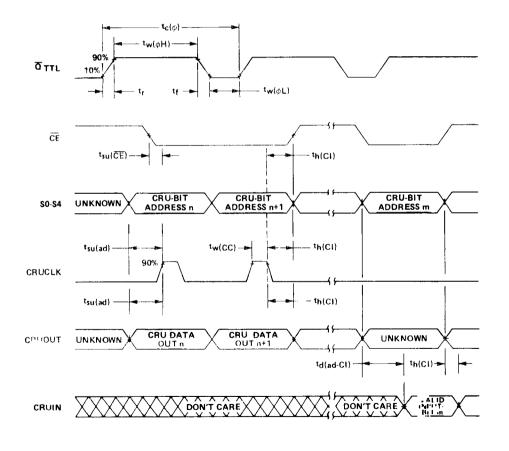

CRU interface timing is shown in Figure 11. The timing for transferring two bits out and one bit in is shown. These transfers would occur during the execution of a CRU instruction. The other cycles of the instruction execution are not illustrated. To output a CRU bit, the CRU-bit address is placed on the address bus A0 through A14 and the actual bit data on CRUOUT. During the second clock cycle a CRU pulse is supplied by CRUCLK. This process is repeated until the number of bits specified by the instruction are completed.

The CRU input operation is similar in that the bit address appears on A0 through A14. During the subsequent cycle the TMS 9900 accepts the bit input data as shown. No CRUCLK pulses occur during a CRU input operation.

FIGURE 9 - TMS 9900 MEMORY BUS TIMING

FIGURE 10 - TMS 9900 HOLD TIMING

9900 FAMILY SYSTEMS DESIGN

#### 3.6 TMS 9900 INSTRUCTION EXECUTION TIMES

Instruction execution times for the TMS 9900 are a function of:

- 1) Clock cycle time,  $t_{c}(\phi)$

- 2) Addressing mode used where operands have multiple addressing mode capability

- 3) Number of wait states required per memory access.

Table 3 lists the number of clock cycles and memory accesses required to execute each TMS 9900 instruction. For instructions with multiple addressing modes for either or both operands, the table lists the number of clock cycles and memory accesses with all operands addressed in the workspace-register mode. To determine the additional number of clock cycles and memory accesses required for modified addressing, add the appropriate values from the referenced tables. The total instruction-execution time for an instruction is:

$\mathsf{T}=\mathsf{t}_{\mathsf{c}}(\phi)(\mathsf{C}{+}(\mathsf{W}{}{\star}\mathsf{M}))$

where:

T = total instruction execution time;

$t_{c}(\phi) = clock cycle time;$

- C = number of clock cycles for instruction execution plus address modification;

- W = number of required wait states per memory access for instruction execution plus address modification;

- M = number of memory accesses.

TABLE 3

INSTRUCTION EXECUTION TIMES

| INSTRUCTION        | CLOCK<br>CYCLES | MEMORY | ADDR        |           |                    | CLOCK       | MEMORY      |         | DORESS |  |  |  |  |  |

|--------------------|-----------------|--------|-------------|-----------|--------------------|-------------|-------------|---------|--------|--|--|--|--|--|

| INSTRUCTION        | CYCLES          | ACCESS | M- 1 (<br>i | · · · · · | INSTRUCTION        | CYCLES<br>C | ACCESS<br>M | Merelia |        |  |  |  |  |  |

| A                  | 14              | 4      | - <u>-</u>  | 1         | LWPI               | 10          | 2           | +       | -      |  |  |  |  |  |

| АВ                 | 14              | 4      | в           | в         | MOV                | 14          | 4           | A       | A      |  |  |  |  |  |

| ABS (MSB = 0)      | 12              | 2      | A           |           | MOVB               | 14          | 4           | B       | B      |  |  |  |  |  |

| (MSB = 1)          | 14              | 3      | Ą           |           | MPY                | 52          | 5           | A       | _      |  |  |  |  |  |

| AI                 | 14              | 4      | _           |           | NEG                | 12          | 3           | A       | _      |  |  |  |  |  |

| ANDI               | 14              | 4      |             |           | OBL                | 14          | 4           |         | -      |  |  |  |  |  |

| B                  | 8               | 2      | А           |           | BSET               | 12          | 1           | _       | -      |  |  |  |  |  |

| BL                 | 12              | 3      | A           | 1.        | BTWP               | 14          | 4           |         |        |  |  |  |  |  |

| BLWP               | 26              | 6      | A           |           | s                  | 14          | 4           | A       | A      |  |  |  |  |  |

| с                  | 14              | 3      | A           | A         | SB                 | 14          | 4           | В       | в      |  |  |  |  |  |

| C8                 | 14              | 3      | B           | 8         | SBO                | 12          | 2           |         | -      |  |  |  |  |  |

| ci                 | 14              | 3      | -           |           | SBZ                | 12          | 2           | _       | -      |  |  |  |  |  |

| CKDF               | 12              | 1      | -           |           | SETO               | 10          | 3           | A       | _      |  |  |  |  |  |

| CKON               | 12              | 1      | _           |           | Shift (C / 0)      | 12+2C       | 3           |         |        |  |  |  |  |  |

| CLR                | 10              | 3      | A           | _         | (C+0, Bits 12- 15  | 12720       | 3           | ~       | i -    |  |  |  |  |  |

| coc                | 14              | 3      | A           | -         | of WRQ_01          | 52          | 4           |         | _      |  |  |  |  |  |

| czc                | 14              | 3      | A           |           | (C=0, Bits 12 15   | 52          | 4           | -       | -      |  |  |  |  |  |

| DEC                | 10              | 3      | A           |           | of WRP_N ≠ 0)      | 20+2N       | 4           | -       |        |  |  |  |  |  |

| DECT               | 10              | 3      | A           |           | SOC                | 14          | 4           |         |        |  |  |  |  |  |

| DIV (ST4 is set)   | 16              | 3      | A           |           | SOCB               | 14          | 4           | в       | A      |  |  |  |  |  |

| DIV (ST4 is reset) | 92-124          | 6      | A           |           | STCR (C 0)         | 60          | 4           |         | в      |  |  |  |  |  |

| IOLE               | 12              | 1      | -           |           | (1+ C+ 7)          |             | 4           | A       | ~~     |  |  |  |  |  |

| INC                | 10              | 3      | -<br>A      | 1         | (C 8)              | 42          |             | В       | -      |  |  |  |  |  |

| INCT               | 10              | 3      | A           |           | (9+ C+ 15)         | 44          | 4           | В       | -      |  |  |  |  |  |

| INV                | 10              | 3      | A           |           | STST               | 58          | 4           | A       | -      |  |  |  |  |  |

| Jump (PC is        | 10              | 5      | ~           |           | STWP               | 8           | 2           |         |        |  |  |  |  |  |

| changed)           | 10              | 1      |             |           | SWPB               | 10          | 2           |         | -      |  |  |  |  |  |

| (PC is not         | 10              |        | -           |           | SZC                | 14          | 4           | A       |        |  |  |  |  |  |

| changed)           | 8               | 1      |             |           | SZCB               | 14          | 4           | B       | A      |  |  |  |  |  |

| LDCR (C · 0)       | 52              | 3      | A           |           | TB                 |             |             |         | 8      |  |  |  |  |  |

| (1. C. B)          | 20+2C           | . 3    | В           |           | X···               | 12          | 2           | -<br>A  | _      |  |  |  |  |  |

| (9 · C· 15)        | 20120           | 3      | A           |           | XOP                | 36          | 2           |         | _      |  |  |  |  |  |

| LI                 | 12              | 3      | <u> </u>    |           | XOR                | 14          | 4           | A       | _      |  |  |  |  |  |

| LIMI               | 16              | 2      | _           |           | , XOR              | 14          | 4           |         | -      |  |  |  |  |  |

| LREX               | 12              | 1      |             |           | 1                  |             |             | 1       |        |  |  |  |  |  |

| RESET function     |                 | 5      |             |           | r                  | +           |             |         |        |  |  |  |  |  |

|                    | 26              |        |             | -         | Undefined op codes | 1           |             |         |        |  |  |  |  |  |

| LOAD function      | 22              | 5      | -           | · ·       | 0000-01FF,0320     | 6           | 1           |         | -      |  |  |  |  |  |

| Interrupt context  |                 |        |             |           | 033F,0C00 0FFF,    |             |             |         |        |  |  |  |  |  |

| switch             | 22              | 5      | -           | -         | 0780-07 F F        | 1           |             | 1       |        |  |  |  |  |  |

\*Execution time is dependent upon the partial quotient after each clock cycle during execution.

\*\*Execution time is added to the execution time of the instruction located at the source address minus 4 clock cycles and 1 memory access time. <sup>†</sup>The letters A and B refer to the respective tables that follow.

9900 FAMILY SYSTEMS DESIGN

#### ADDRESS MODIFICATION - TABLE A

|                                                     | CLOCK | MEMORY<br>ACCESSES |

|-----------------------------------------------------|-------|--------------------|

| ABB ALCONING MODE                                   | c     | M                  |

| WR (T <sub>S</sub> or T <sub>D</sub> = 00)          | 0     | 0                  |

| WR indirect (T <sub>S</sub> or T <sub>D</sub> = 01) | 4     | 1                  |

| WR indirect auto-                                   |       |                    |

| increment (T <sub>S</sub> or T <sub>D</sub> = 11)   | 8     | 2                  |

| Symbolic ( $T_S$ or $T_D = 10$ ,                    |       |                    |

| S or D = 0)                                         | 8     | 1                  |

| Indexed (T <sub>S</sub> or T <sub>D</sub> = 10,     |       |                    |

| S or D ≠ 0)                                         | 8     | 2                  |

|  | ADDRESS | MODIFICATION - | TABLE B |

|--|---------|----------------|---------|

|--|---------|----------------|---------|

|                                                     | CLOCK  | MEMORY   |

|-----------------------------------------------------|--------|----------|

| ADD RESSING MODE                                    | CYCLES | ACCESSES |

|                                                     | с      | м        |

| WR (T <sub>S</sub> or T <sub>D</sub> = 00)          | 0      | o        |

| WR indirect (T <sub>S</sub> or T <sub>D</sub> = 01) | 4      | 1 1      |

| WR indirect auto-                                   |        |          |

| increment (T <sub>S</sub> or T <sub>D</sub> = 11)   | 6      | 2        |

| Symbolic (T <sub>S</sub> or T <sub>D</sub> = 10,    |        |          |

| S or D = 0)                                         | 8      | 1        |

| Indexed (Ts or T <sub>D</sub> = 10,                 |        |          |

| S or D ≠ 0)                                         | 8      | 2        |

As an example, the instruction MOVB is used in a system with  $t_{C}(\phi) = 0.333 \,\mu s$  and no wait states are required to access memory. Both operands are addressed in the workspace register mode:

$T = t_c(\phi)(C+(W*M)) = 0.333 (14+(0*4)) = 4.662 \ \mu s$

If two wait states per memory access were required, the execution time is:

$T = 0.333 (14+(2\cdot4)) \mu s = 7.326 \mu s.$

If the source operand was addressed in the symbolic mode and two wait states were required:

$T = t_{C}(\phi) (C+(W * M))$ C = 14 + 8 = 22 M = 4 + 1 = 5 T = 0.333 (22+(2\*5))  $\mu$ s = 10.656  $\mu$ s.

#### 4. TMS 9900 ELECTRICAL SPECIFICATIONS

# 4.1 ABSOLUTE MAXIMUM RATINGS OVER OPERATING FREE-AIR TEMPERATURE RANGE (UNLESS OTHERWISE NOTED)\*

| Supply voltage, V <sub>CC</sub> (see Note 1) . |  |  |   |  |  |  |  |  |  |  |  |         | -0.3 to 20 V        |

|------------------------------------------------|--|--|---|--|--|--|--|--|--|--|--|---------|---------------------|

| Supply voltage, VDD (see Note 1) .             |  |  |   |  |  |  |  |  |  |  |  |         |                     |

| Supply voltage, VSS (see Note 1)               |  |  |   |  |  |  |  |  |  |  |  |         | -0.3 to 20 V        |

| All input voltages (see Note 1)                |  |  |   |  |  |  |  |  |  |  |  |         | 0.3 to 20 V         |

| Output voltage (with respect to VSS)           |  |  |   |  |  |  |  |  |  |  |  |         | -2 V to 7 V         |

| Continuous power dissipation                   |  |  |   |  |  |  |  |  |  |  |  |         | 1.2 W               |

| Operating free-air temperature range           |  |  | • |  |  |  |  |  |  |  |  | •       | <b>0</b> °C to 70°C |

| Storage temperature range                      |  |  |   |  |  |  |  |  |  |  |  | <br>-59 | 5°C to 150°C        |

<sup>\*</sup>Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other conditions beyond those indicated in the "Recommended Operating Conditions" section of this specification is not implied, Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

NOTE 1 Under absolute maximum ratings voltage values are with respect to the most negative supply, V<sub>BB</sub> (substrate), unless otherwise noted. Throughout the remainder of this section, voltage values are with respect to V<sub>SS</sub>.

# TMS 9900 ELECTRICAL SPECIFICATIONS

#### 4.2 RECOMMENDED OPERATING CONDITIONS

|                                                          | MIN               | NOM | MAX                | UNIT |

|----------------------------------------------------------|-------------------|-----|--------------------|------|

| Supply voltage, VBB                                      | -5.25             | -5  | -4.75              | ٧    |

| Supply voltage, V <sub>CC</sub>                          | 4.75              | 5,  | 5.25               | V    |

| Supply voltage, VDD                                      | 11.4              | 12  | 12.6               | ν    |

| Supply voltage, V <sub>SS</sub>                          |                   | 0   |                    | v    |

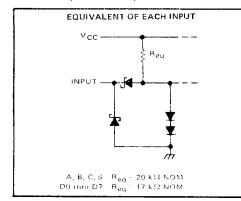

| High-level input voltage, VIH (all inputs except clocks) | 2.2               | 2.4 | V <sub>CC</sub> +1 | v    |

| High-level clock input voltage, VIH( $\phi$ )            | V <sub>DD-2</sub> |     |                    | V    |

| Low-level input voltage, VIL (all inputs except clocks)  | -1                | 0.4 | 0.8                | v    |

| Low-level clock input voltage, $V_{ L(\phi)}$            | -0.3              | 0.3 | 0.6                | V    |

| Operating free-air temperature, TA                       | 0                 |     | 70                 | °C   |

# 4.3 ELECTRICAL CHARACTERISTICS OVER FULL RANGE OF RECOMMENDED OPERATING CONDITIONS (UNLESS OTHERWISE NOTED)

|                    | PARA             | METER                                                  | TEST CONDITIONS                                                       | MIN | TYP <sup>†</sup> | MAX  | UNIT |

|--------------------|------------------|--------------------------------------------------------|-----------------------------------------------------------------------|-----|------------------|------|------|

|                    |                  | Data bus during DBIN                                   | $V_{I} = V_{SS}$ to $V_{CC}$                                          |     | ±50              | ±100 |      |

| ų                  | Input current    | WE, MEMEN, DBIN, Address<br>bus, Data bus during HOLDA | $V_{I} = V_{SS}$ to $V_{CC}$                                          |     | ±50              | ±100 | μA   |

|                    |                  | Clock                                                  | V <sub>I</sub> = -0.3 to 12.6 V                                       |     | ±25              | ±75  | 1    |

|                    |                  | Any other inputs                                       | VI = VSS to VCC                                                       |     | ±1               | ±10  | L    |

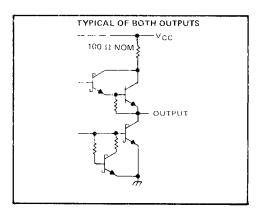

| ∨он                | High-level outp  | out voltage                                            | lo = -0.4 mA                                                          | 2.4 |                  | VCC  | V    |

|                    |                  |                                                        | lo = 3.2 mA                                                           |     |                  | 0.65 |      |

| VOL                | Low-level outp   |                                                        | l <sub>0</sub> = 2 mA                                                 |     |                  | 0.50 | 1 °. |

| BB (av)            | Supply current   | from V <sub>BB</sub>                                   |                                                                       |     | 0.1              | 1    | mA*  |

| CC(av)             | Supply current   | from VCC                                               |                                                                       | _   | 50               | 75   | mA*  |

| IDD(av)            | Supply current   | from VDD                                               |                                                                       |     | 25               | 45   | mA*  |

| Ci                 | Input capacitar  | nce (any inputs except<br>bus)                         | VBB =5, f = 1MHz,<br>unmeasured pins at VSS                           |     | 10               | 15   | ρF   |

| C <sub>i(φ1)</sub> | Clock-1 input o  | capacitance                                            | V <sub>BB</sub> =5, f = 1MHz,<br>unmeasured pins at V <sub>SS</sub>   |     | 100              | 150  | pF   |

| С <sub>і(ф2)</sub> | Clock-2 input    | capacitance                                            | V <sub>BB</sub> =5, f = 1MHz,<br>unmeasured pins at V <sub>SS</sub>   |     | 150              | 200  | ρF   |

| C <sub>i(φ3)</sub> | Clock-3 input of | capacitance                                            | V <sub>BB</sub> = -5, f = 1MHz,<br>unmeasured pins at V <sub>SS</sub> |     | 100              | 150  | pF   |

| С <sub>і(ф4)</sub> | Clock-4 input o  | capacitance                                            | V <sub>BB</sub> = -5, f = 1MHz,<br>unmeasured pins at V <sub>SS</sub> |     | 100              | 150  | pF   |

| CDB                | Data bus capac   | itance                                                 | V <sub>BB</sub> = -5, f = 1MHz,<br>unmeasured pins at V <sub>SS</sub> |     | 15               | 25   | pF   |

$^\dagger$  All typical values are at T  $_A$  = 25  $^\circ$  C and nominal voltages. \* D.C. Component of Operating Clock

84

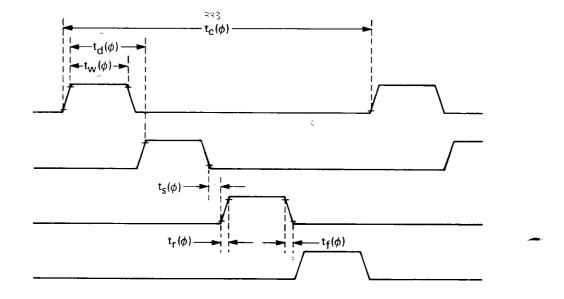

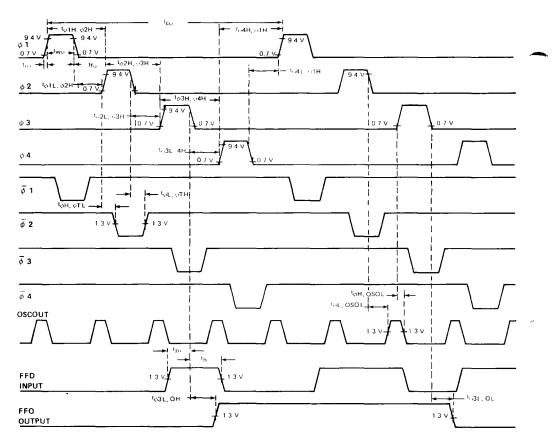

#### 4.4 TIMING REQUIREMENTS OVER FULL RANGE OF RECOMMENDED OPERATING CONDITIONS

|                   | PARAMETER                                                    | MIN | NOM | MAX | UNIT | ٦ |

|-------------------|--------------------------------------------------------------|-----|-----|-----|------|---|

| <sup>t</sup> c(φ) | Clock cycle time                                             | 300 | 333 | 500 | ns   | 1 |

| <sup>t</sup> r(φ) | Clock rise time                                              | 5   | 12  |     | ns   |   |

| <sup>t</sup> f(φ) | Clock fall time                                              | 10  | 12  |     | ns   |   |

| tw(φ)             | Clock pulse width, high level                                | 40  | 45  | 100 | ns   | 1 |

| t <sub>s(φ)</sub> | Clock spacing, time between any two adjacent clock pulses    | 0   | 5   |     | ns   | ٦ |

| <sup>t</sup> d(φ) | Time between rising edge valid any two adjacent clock pulses | 73  | 83  |     | ns   | 1 |

| tsu               | Data or control setup time before clock 1                    | 30  |     |     | ns   | 1 |

| th                | Data hold time after clock 1                                 | 10  |     |     | ns   | 7 |

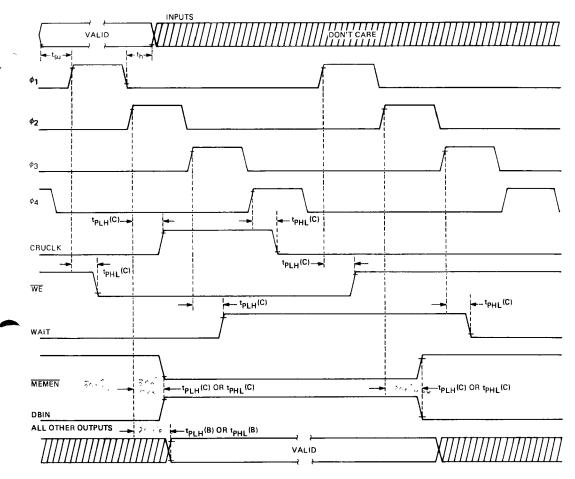

#### 4.5 SWITCHING CHARACTERISTICS OVER FULL RANGE OF RECOMMENDED OPERATING CONDITIONS

|                                              | PARAMETER                                       | TEST<br>CONDITIONS | MIN | түр | MAX | UNIT |

|----------------------------------------------|-------------------------------------------------|--------------------|-----|-----|-----|------|

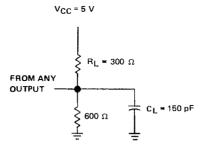

| tPLH (B) or tPHL (B)                         | All other outputs                               | C: - 200 - F       |     | 20  | 40  | ns   |

| <sup>t</sup> PLH (C) <sup>or t</sup> PHL (C) | Propagation delay CRUCLK, WE, MEMEN, WAIT, DBIN | CL = 200 pF        |     |     | 30  | ns   |

FIGURE 12 - CLOCK TIMING

#### **Product Data Book**

# TMS 9900 ELECTRICAL SPECIFICATIONS

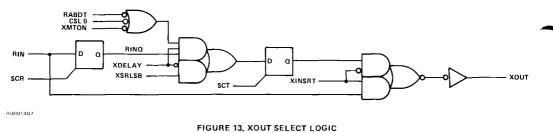

FIGURE 13-SIGNAL TIMING

8.

#### **TMS 9900-40 ELECTRICAL SPECIFICATIONS**

# ABSOLUTE MAXIMUM RATINGS OVER OPERATING FREE-AIR TEMPERATURE RANGE (UNLESS OTHERWISE NOTED)'

| Supply voltage, V <sub>CC</sub> (see Note 1)      | -0.3 to 20 '  |

|---------------------------------------------------|---------------|

| Supply voltage, V <sub>DD</sub> (see Note 1)      | -0.3 to 20 V  |

| Supply voltage, V <sub>SS</sub> (see Note 1)      | -0.3 to 20 V  |

| All input voltages (see Note 1)                   | -0.3 to 20 V  |

| Output voltage (with respect to V <sub>SS</sub> ) | . −2 V to 7 V |

| Continuous power dissipation                      | 1.2 W         |

| Operating free-air temperature range              |               |

| Storage temperature range                         | 55°C to 150°C |

"Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other conditions beyond those indicated in the "Recommended Operating Conditions" section of this specification is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

NOTE 1: Under absolute maximum ratings voltage values are with respect to the most negative supply, V<sub>BB</sub> (substrate), unless otherwise noted. Throughout the remainder of this section, voltage values are with respect to V<sub>SS</sub>

#### RECOMMENDED OPERATING CONDITIONS

|                                                          | MIN                | NOM | MAX                | UNIT |

|----------------------------------------------------------|--------------------|-----|--------------------|------|

| Supply voltage, V <sub>BB</sub>                          | -5.25              | -5  | -4.75              | v    |

| Supply voltage, V <sub>CC</sub>                          | 4.75               | 5   | 5.25               | V    |

| Supply Voltage, V <sub>DD</sub>                          | 11.4               | 12  | 12.6               | V    |

| Supply voltage, Vss                                      |                    | 0   |                    | V    |

| High-level input volrage, VIH (all inputs except clocks) | 2.2                | 2.4 | V <sub>cc</sub> +1 | V    |

| High-level clock input voltage, VIH(0)                   | V <sub>DD</sub> -2 |     | VDD                | V    |

| Low-level input voltage, VIL (all inputs except clocks)  | - 1                | 0.4 | 0.8                | V    |

| Low-level clock input voltage, VIL(#)                    | - 0.3              | 0.3 | 0.6                | V    |

| Operating free-air temperature, T <sub>A</sub>           | 0                  |     | 70                 | °C   |

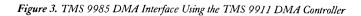

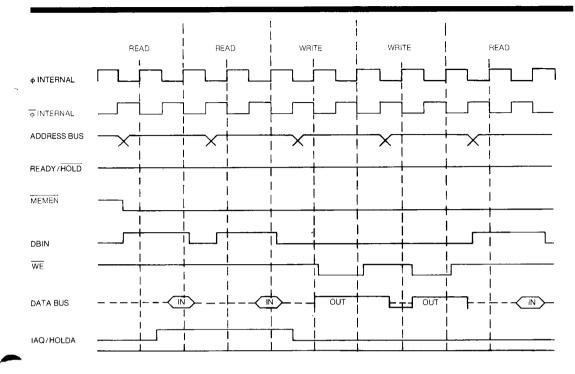

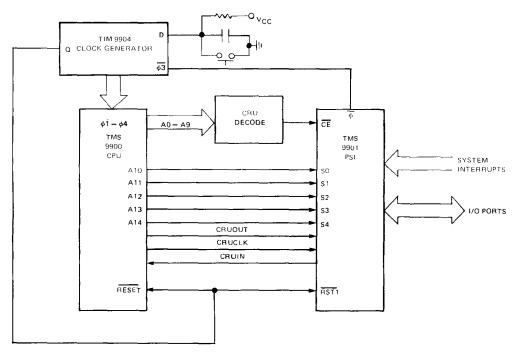

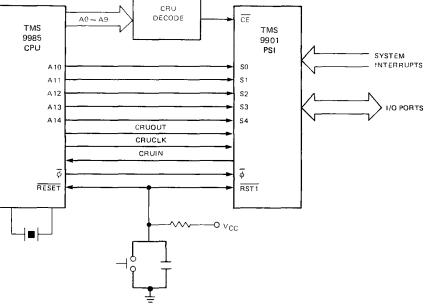

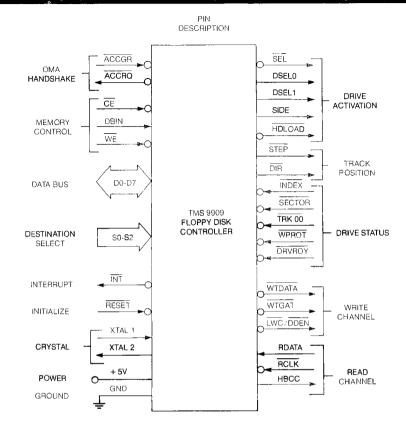

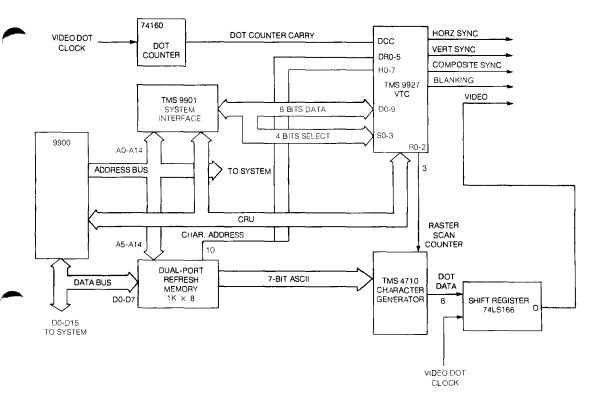

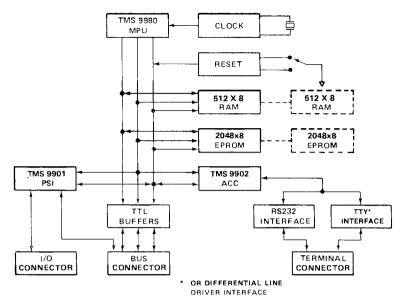

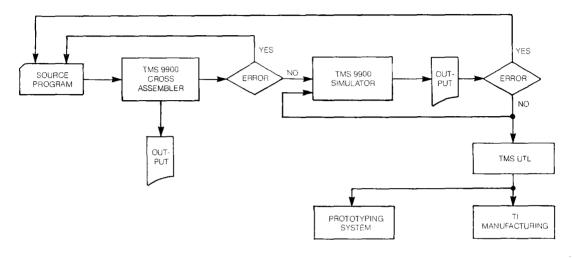

DESIGN GOAL